ZYNQ板子本身芯片有PS_POR_B和和PS_SRST 硬件和软件复位信号了,所以硬件上没必要额外在PL端再增加复位信号了,那如何为PL的程序增加RST复位信号呢,这边提供了三种方式 可供选择

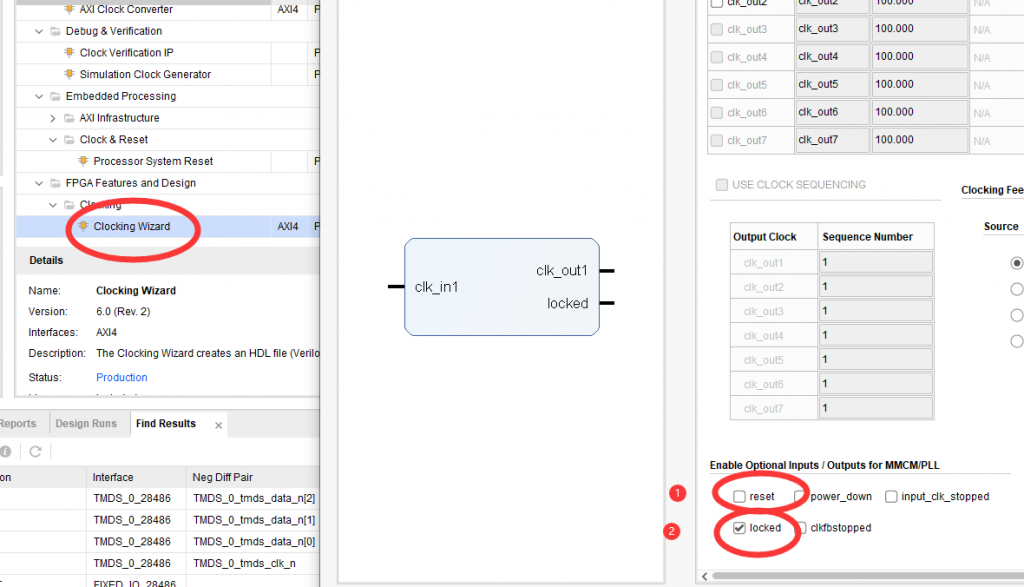

方法一 PLL的locked 充当复位信号

用FPGA的PLL 模块的locked信号来充当RST_N复位信号, Locked信号是用来观察pll输出时钟是否和输入时钟锁定。当锁定时,这个Locked信号就由低电平变为高电平,而这个信号也可以为我们充当rst_n信号来使用 clock wizard默认就会打开这个locked信号(如果我们用locked来充当复位信号,代表输入我们不使用其他复位信号,所以 这里可以直接关闭输入的reset信号)

方法二 用计数器加initial的方式充当复位信号

我们也可以为自己写一个1秒钟的复位信号(可以更短)

这里我们用到initial 来初始化计数器(因为如果没有复位信号,上电瞬间reg 的值可能是随机的,但是增加了initial,上电后reg的值会被初始化为我们给定的值)具体程序如下

parameter T1MS = 26'd50_000_000 ; //50M晶振时钟

reg [25:0]time_count;//时钟计数器

reg rst_n;

initial begin

time_count=26'd0;

rst_n=1'b0;

end

always@(posedge clk)

if(time_count<T1MS)begin

time_count<=time_count+1'b1;

end

else rst_n<=1'b1;

程序很好理解, initial 块里 初始化了 time_count的值为0,初始化复位信号rst_n的值为0

然后在always块中 当时间计数没满一秒的时候 time_count一直自增, 当计数器计数满一秒钟后,计数器停止计数,并且寄存器rst_n由低电平 变成了高电平。 这里的rst_n 我们就可以拿来充当各个其他always 块的复位信号使用

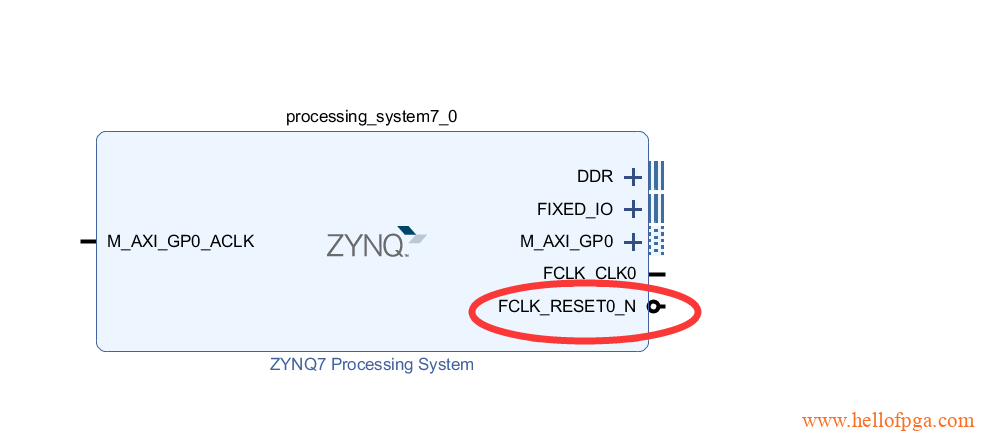

方法三 用ZYNQ模块的复位信号(比较常用)

因为 不论是TF启动,还是 程序固化到 FLASH启动,我们都必须添加ZYNQ核才能完成上电加载启动的工作,可以这么说只要一个完整的工程,都少不了ZYNQ核,所以这里直接用ZYNQ PS现成的复位信号是最方便也是最理所当然的。 在blockdesign 里添加zynq 核后,zynq核默认就带了FCLK_RESET0_N信号,这个信号直接可以充当各个模块的复位信号使用。

当然还有 Block Design 自动生成的System reset 模块产生的复位信号也是可以使用的。

添加复位的方法还有很多种,大家也可以自行脑洞自行尝试