本工程将记录在SDK环境下调用官方demo来实现USB的slave(device)功能测试

- 此章节内容适用于Smart ZYNQ SP SP2版的板子 ( 不包含Smart ZYNQ 标准版 ),如是标准版或本站其他板子请看对应板子目录

- Smart ZYNQ SL版不带USB资源,所以本工程不适用于SL版的主板

- 本文在 vivado2018.3版本上演示

ZYNQ的USB可以同时充当USB HOST,和USB DEVICE(SLAVE)的角色功能非常强大,板子上同时保留了USB HOST的接口,和USB DEVICE的接口,USB功能大多数情况都是在linux下使用的,在arm裸机下使用的资料非常的少,好在官方为我们保留了一个USB DEVICE的SDK Demo,我们可以通过这个demo去熟悉整个usb项目的创建流程,具体操作如下。

一、工程创建

工程创建的过程可以参考实验一中的内容,这里不详细描述了。基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验一 GPIO之用EMIO方式点亮LED(完整图文) (芯片型号选XC7Z020CLG484-1)

二、Vivado 中的设置

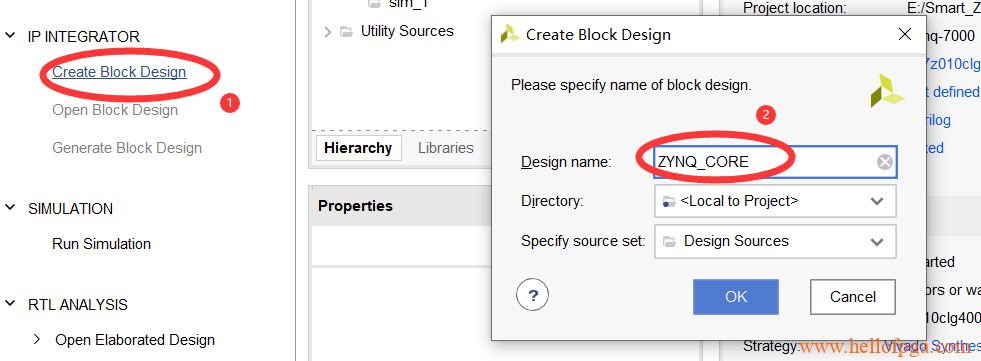

1)IP INTEGRATOR→Create Block Design,在弹出的对话框中输入设计名,最后点击“OK”,如下图所示

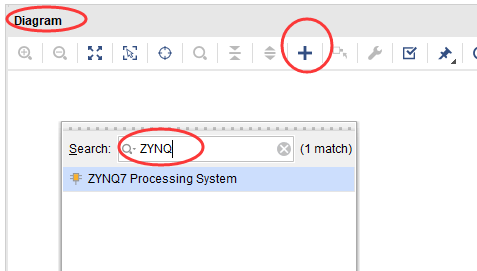

2)在右侧的窗口里 ,点击加号,在选择框里搜索ZYNQ,并找到ZYNQ7 PROCESSING SYSTEM ,双击并打开

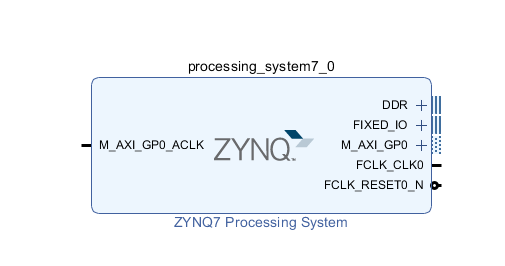

3) 软件自动生成了一个 zynq的block 如下图所示,接下来要做一些相应的设置,双击下图中的ZYNQ核

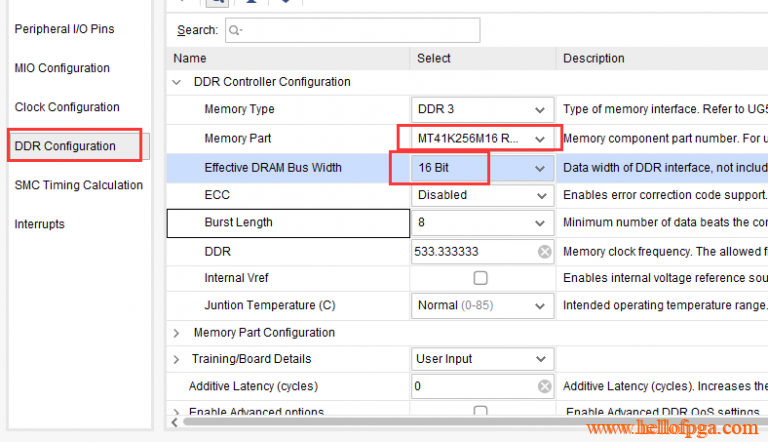

4)依次在弹窗里找到DDR Configuration→DDR Controller Configuration→DDR3,在Memory Part下拉菜单中根据自己板子上的DDR来选择相应的DDR3,本实验所用到型号:MT41K256M16RE-125,数据位宽选择16bit 最后点击“OK”,如下图所示。

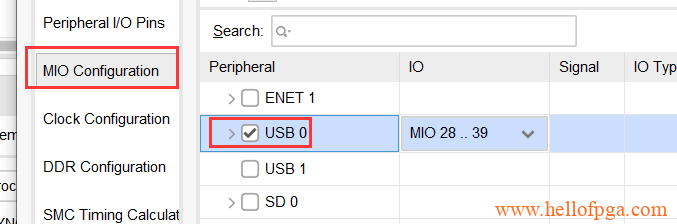

5) 使能zynq的USB0功能

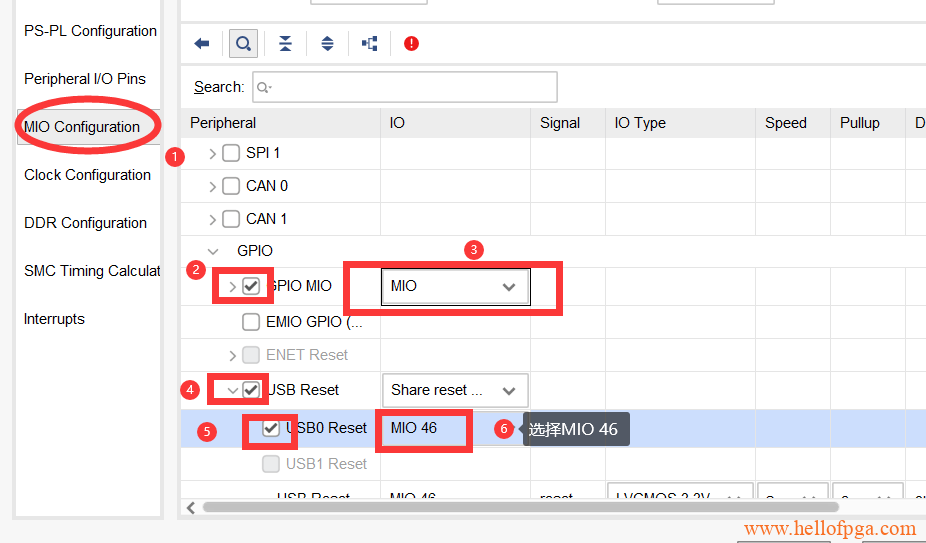

6) 另外 由于我们的USB PHY的信号是接在mio的46脚上 所以这里同样需要使能 MIO的USB RST信号(系统同时会默认勾选I2C复位 ,可以关闭)

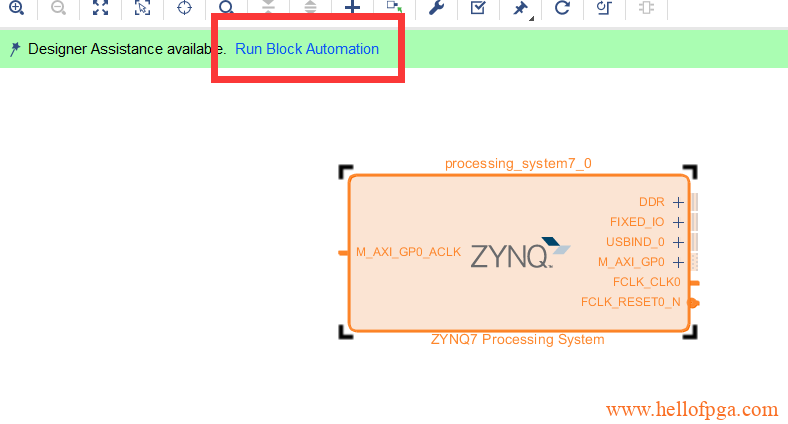

7) 随后点OK 保存修改,并点击“Run Block Automation”如下图所示。在弹出的选项中保持默认,点击“OK”,即可完成对ZYNQ7 Processing System的配置

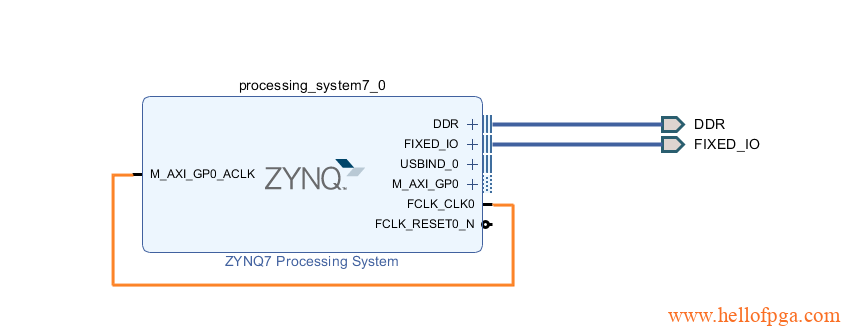

8) 连接AXI的时钟(AXI默认开启的,这里用不到AXI,也可以去设置里关闭AXI功能,就不需要连接了)

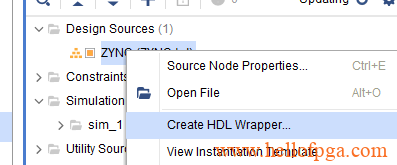

9) 在source→Design Source ,右键我们创建的BLOCK工程,点击create HDL wrapper,打包BLOCK文件并生成.v代码

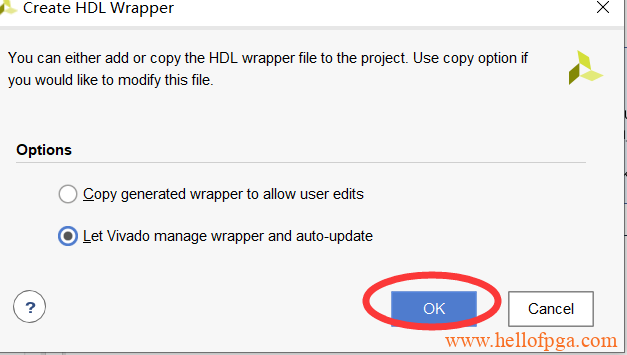

在弹出的对话框里保持默认

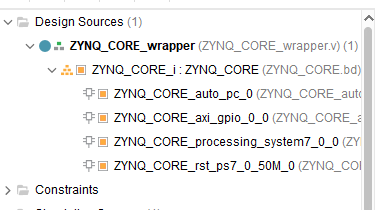

软件自动为我们生成HDL文件

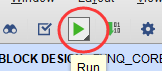

10) 点击绿色箭头RUN 对代码进行编译

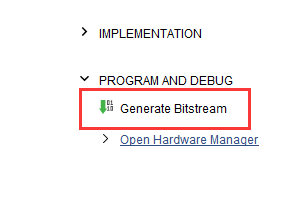

11) 生成bit文件 :按下Generate Bitstream 完成综合以及生成bit文件,等待弹出综合完成的窗口

三、SDK部分设计

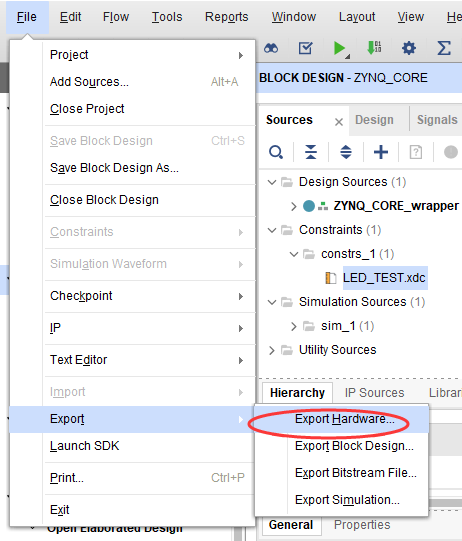

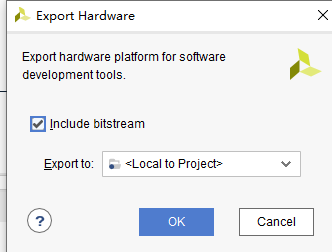

1)File→Export→Export hardware…,在弹出的对话框中勾选“include bitstream”,点击“OK”确认,如下图所示。

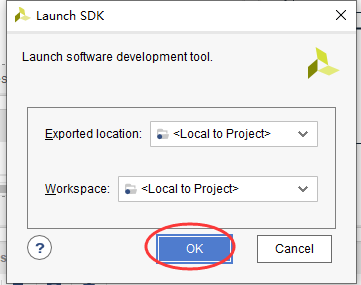

2)File→Lauch SDK,在弹出的对话框中,保存默认,点击“OK”,如下图所示。

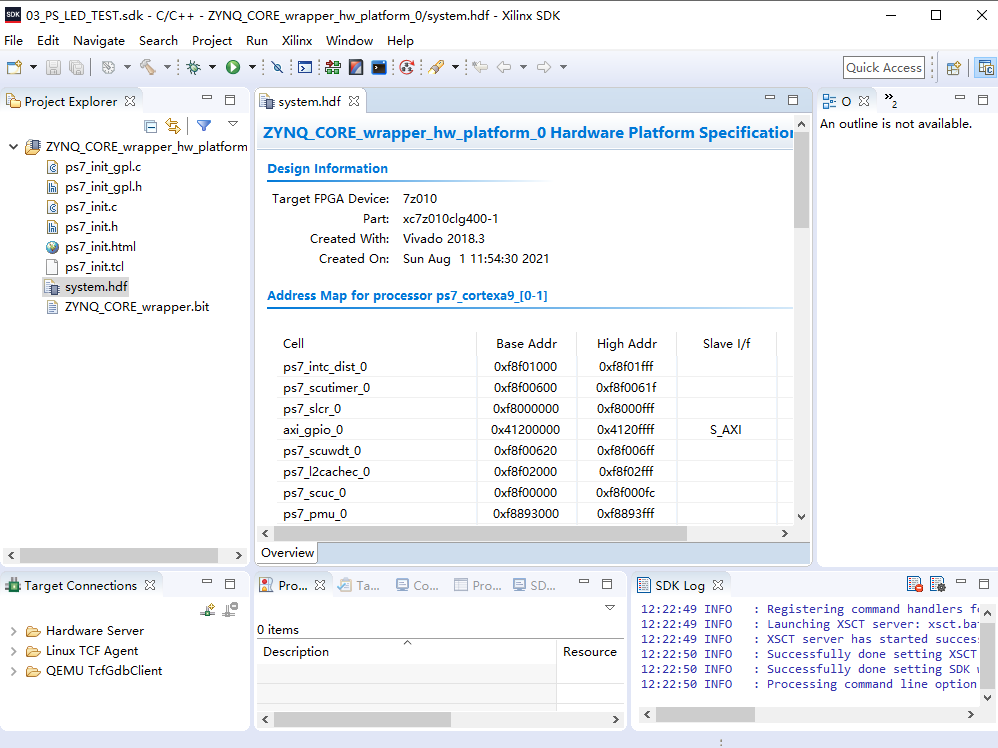

系统将自动打开SDK开发环境

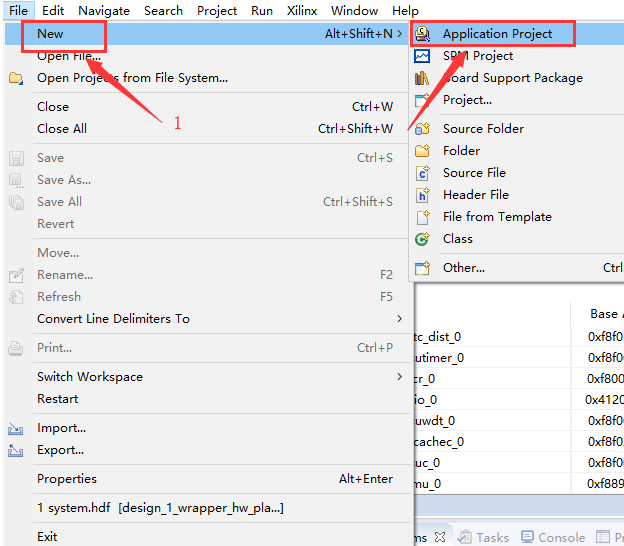

3)新建一个工程 file→new→Application Project,来新建一个“Application Project”,如下图所示。

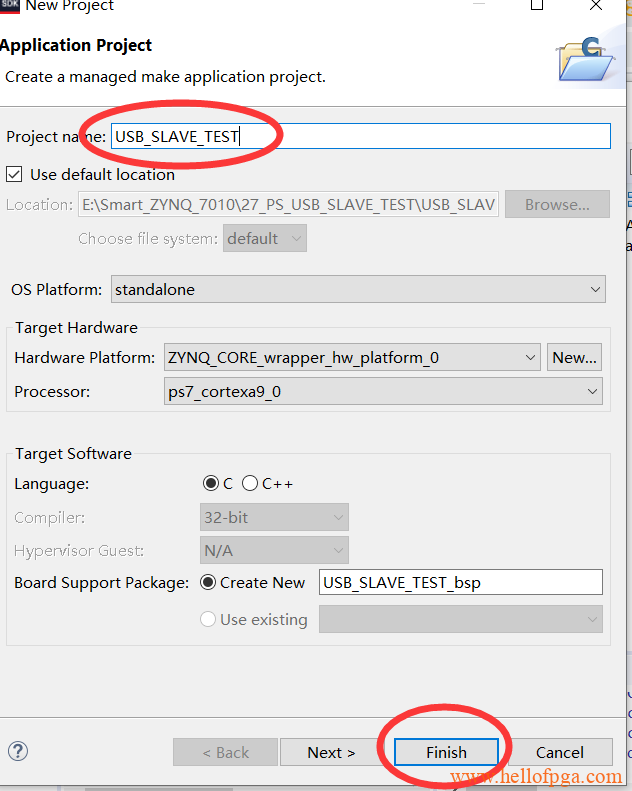

4)在新建工程名中输入自己的工程名称,点击NEXT

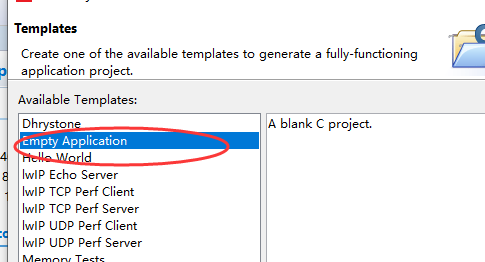

5)选择空工程,点击完成FINISH

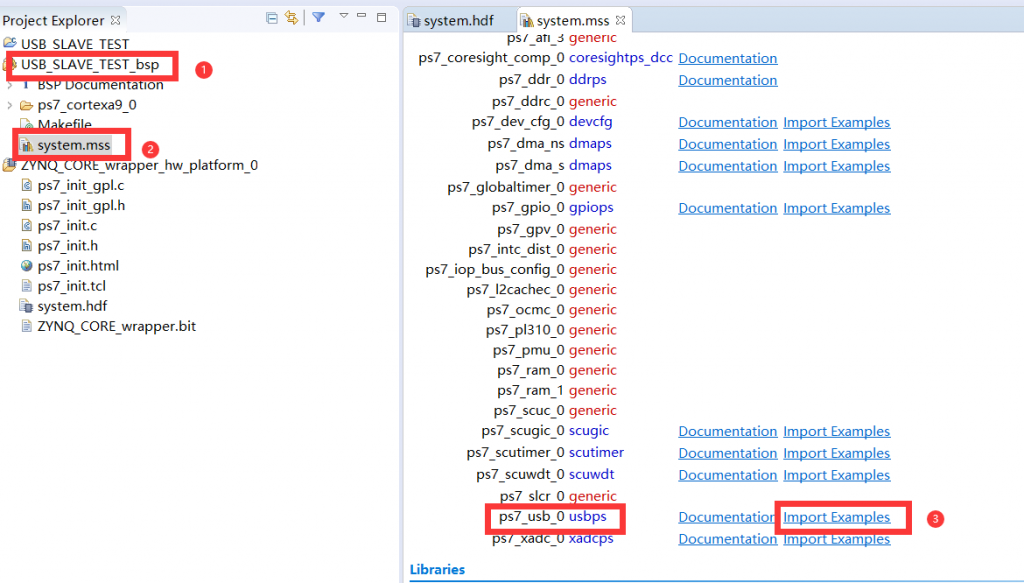

6)之后SDK会为我们创建一个空的工程,这里我们只需要用到bsp就够,如下图所示,展开BSP目录,点击system.mss文件,在右侧选择导入usbps的 demo并导入

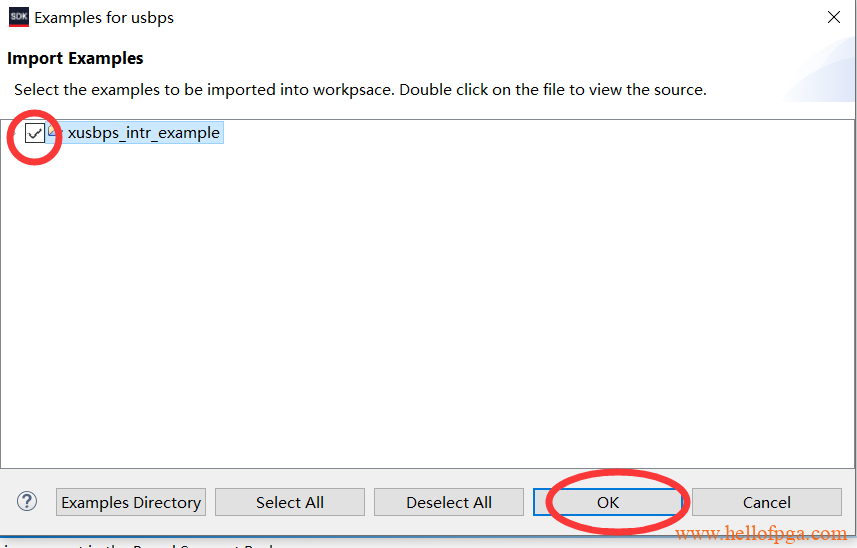

勾选工程,然后点击ok

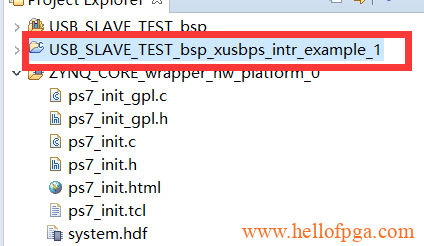

之后系统会自动导入usb的demo,,如下图所示

四、下载和调试

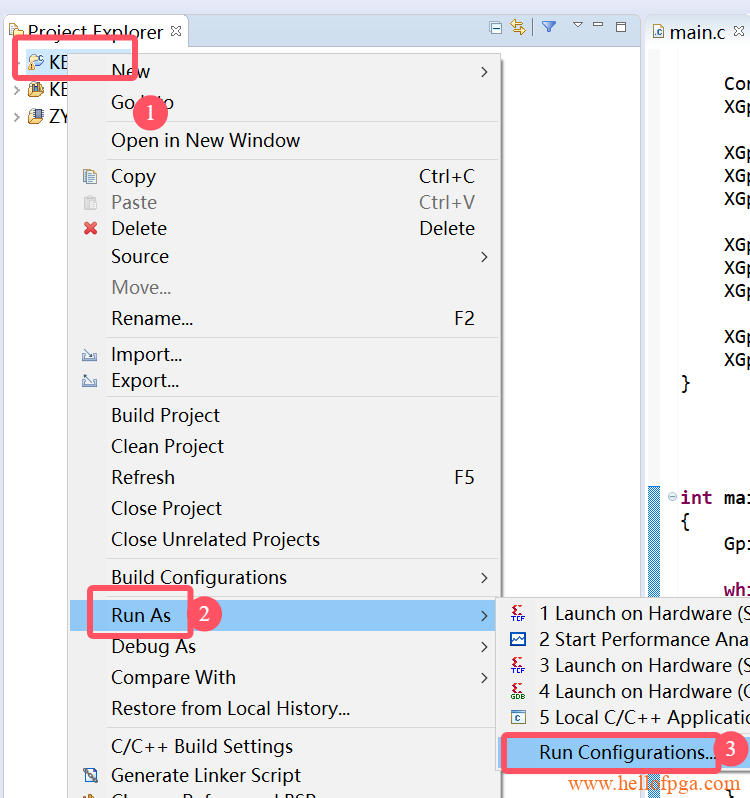

1)先用USB线将板子的JTAG口和电脑连接新创建的工程最好先对Run as 进行配置:右键工程,并点选Run As -> Run Configurations

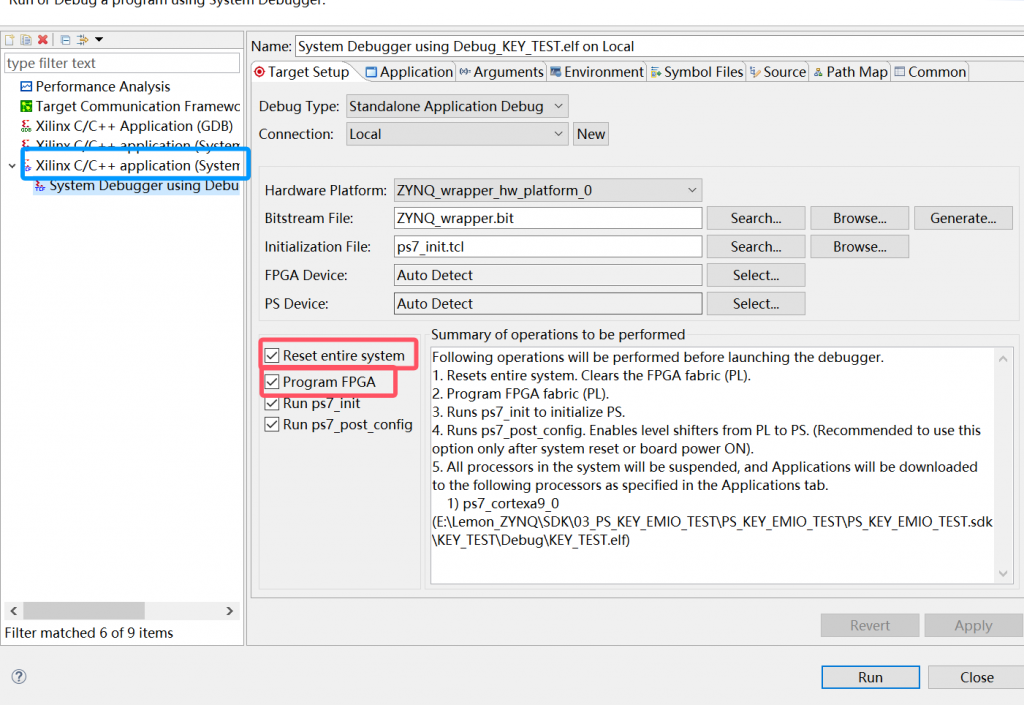

2) 在弹出的窗口中对Reset entire system 和 Program FPGA两个选项进行勾选操作,这样就不会出现下载程序debug的时候概率性不工作的问题了。(这样操作后系统会自动对FPGA进行配置,不需要按之前工程手动对FPGA进行编程了)

PS如果没有出现下图对话框,可以直接双击左侧的applicationo (System Debugger)。

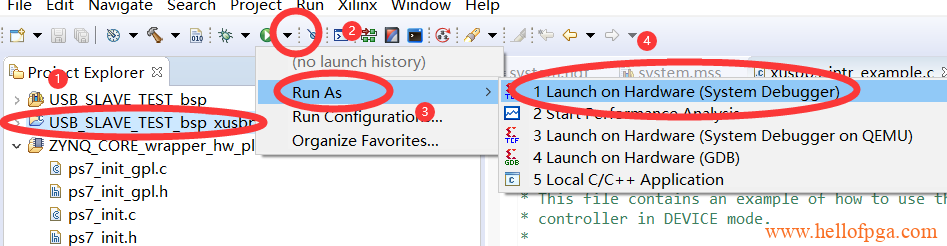

3)选中我们生成的USB工程 展开绿色箭头(RUN)右边的图标,选择Run As→1 Launch on Hardware(System Debugger)

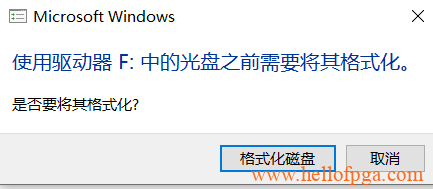

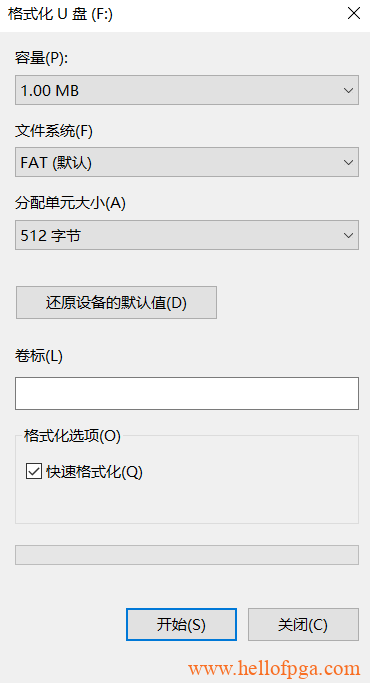

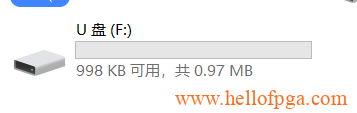

3)用另一根TYPE C数据线连将我们板子上的USB SLAVE口和电脑连接,此时我们可以看到电脑出现了一个1MB的U盘,并提示是否格式化这个U盘(这里选择格式化)

之后电脑就出现了一个由DDR RAM虚拟出来的1MB大小的U盘了(可以像正常U盘一样复制粘贴文件),注意这个U盘断电数据会丢失请不要放重要文件。

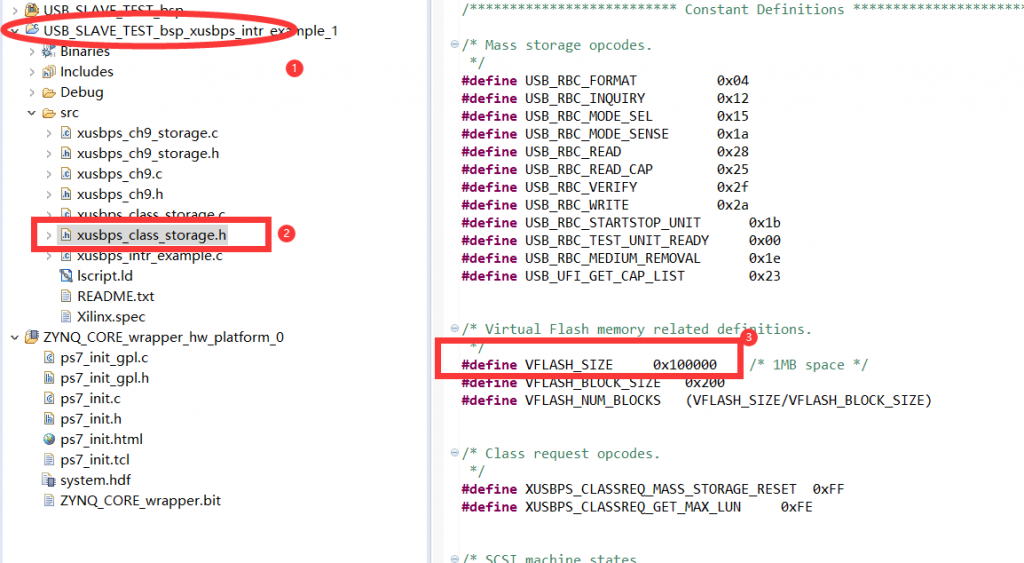

五、修改虚拟U盘的容量大小介绍

测试demo默认的U盘容量只有1MB,这个容量是可以修改的,通过修改 storage.h可以调整这个U盘的大小(请不要接近或者超过板子上DDR容量的大小)

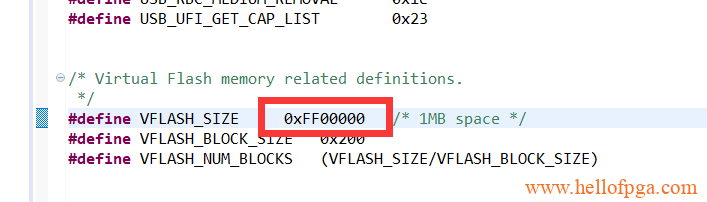

比如说我们将值改成0xFF00000 就可以得到一个255MB的虚拟U盘

以上就是本次USB_SLAVE的功能演示,ZYNQ的 USB 功能远不止这些, 官方SDK 只是提供了一个演示demo,如果要做slave方面的裸机相关应用可以深入研究这个demo , Host功能将在后续petalinux的章节做演示。

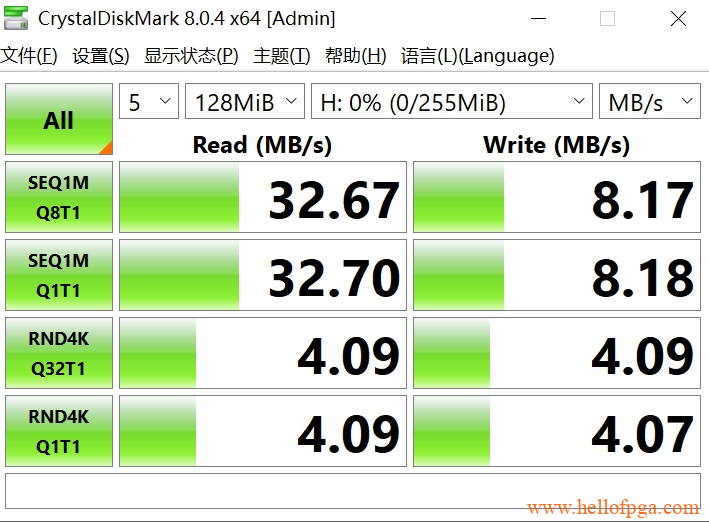

我们用硬盘测速工具来对这个虚拟U盘进行测速,结果如下图所示:

- 本文的完整工程下载:11_PS_USB_SLAVE_TEST

- VIVADO的版本:2018.3

- 工程创建目录:E:\Smart_ZYNQ_SP_SL\SDK\11_PS_USB_SLAVE_TEST

- 工程适用主板: Smart ZYNQ (SP / SP2) (不适用于Smart ZYNQ 标准版 )