介绍Tiny ZYNQ 使用PL 晶振正常设置的管脚进行编译时候会报错的问题的决绝方法

1.问题产生的原因

硬件设计中时钟这块有存在一个不合理的地方,不过不影响使用(FPGA 任意管脚都可以作为信号时钟输入端用),只是特定的时钟脚会默认接入系统时钟总线上,不过 普通IO口 也可以接入到系统时钟的总线上

问题的产生是因为FPGA 的PL部分晶振 接到了 芯片的普通IO了(K18脚),而不是MRCC SRCC,所以在这里需要在约束文件中增加一行代码,让普通IO也能作为时钟输入用

2. 具体操作如下:

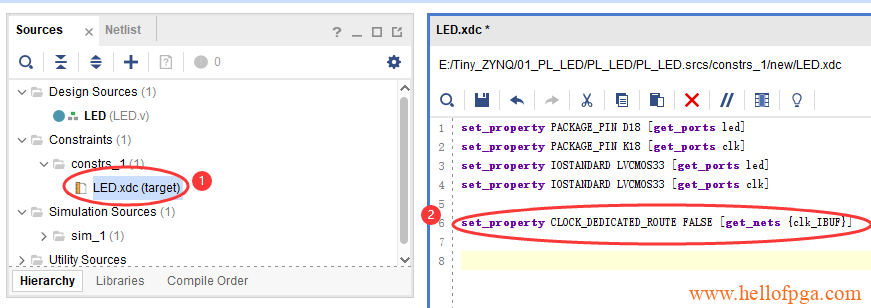

a. 打开工程的xdc约束文件(和管脚约束文件可以是同一个文件,如果没有先创建一个约束文件即可),在约束文件里增加一行代码,代码如下

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets {clk_IBUF}]

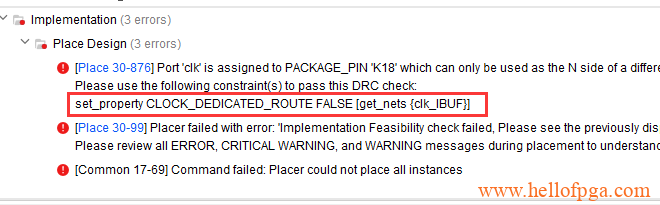

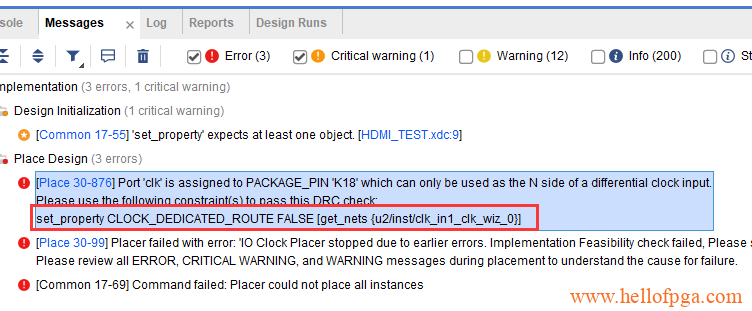

备注:(可能有时候名称上不是 clk_IBUF ,具体看综合时候的报错内容,报错的内容会提示 需要添加什么) 如下面两张图所示,一般如果是本文描述的报错 都会提示怎么进行修改的

另外 clk_IBUF的名称有可能是 大写CLK_IBUF 或者小写clk_IBUF的也可能是其他名称,具体看程序里的名字用的是什么,或者也可以通过系统综合的时候报错的提示来进行修改

b. 之后点击保存,对约束文件进行保存,剩下的操作 和正常没区别

3.题外话关于时钟本身

ZYNQ PL部分的时钟 可以由两种方式提供,一种是 PL端接时钟芯片 ,就是我们电路上的方式

另一种是 用PS 来提供时钟(该方法在项目上比较常用,可以省略一个PL端的晶振,方法可以参看工程3 http://www.hellofpga.com/index.php/2022/10/05/1233/

方法1 的优势是简单 不需要PS的介入(但是如果后面要对程序进行固化,即断电重新启动,那方法1也需要PS 的控制才能启动,所以PS 最终也省不了)

方法2的优势就是 电路成本简单,可以省去一个PL晶振,但是方法2比方式1会略微复杂一点点