程序员的第一个程序都是helloword, 在FPGA领域,点亮一个LED灯的意义相当于helloword,你可以在过程中了解项目从创建到运行的完整流程,下面我用图文来详细介绍每一步的操作。

- 此章节内容适用于Smart ZYNQ SP SP2和 SL 版的板子 ( 不包含Smart ZYNQ 标准版 ),如是标准版或本站其他板子请看对应板子目录

- 本文在 vivado2018.3版本上演示

一、 新建Vivado工程

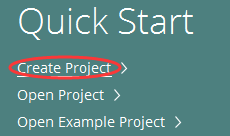

1) 新建一个VIVADO 工程,打开软件 选中Create Project, 如下图所示

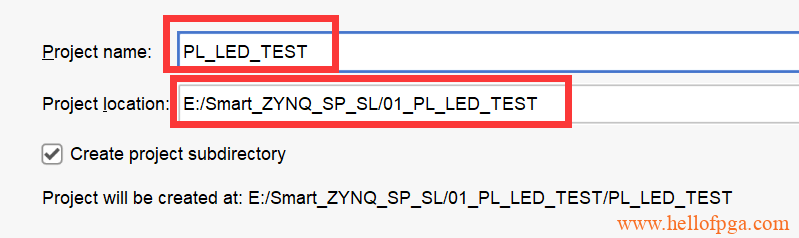

2)点击NEXT ,在出现的第二个对话框“Project name”中输入工程名;在“Project location”中选择保存路径;勾选“Create project subdirectory”,最后点击“Next” 备注,所有的路径均不能出现中文名称

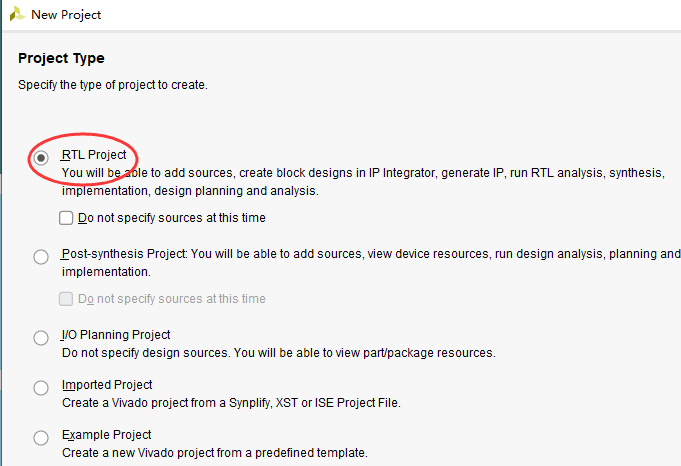

3)点击 RTL PROJECT 选项,点击NEXT

4) 第四步Add Sources 选项直接留空,NEXT

5)第五步Add Constraints 选项直接留空,NEXT

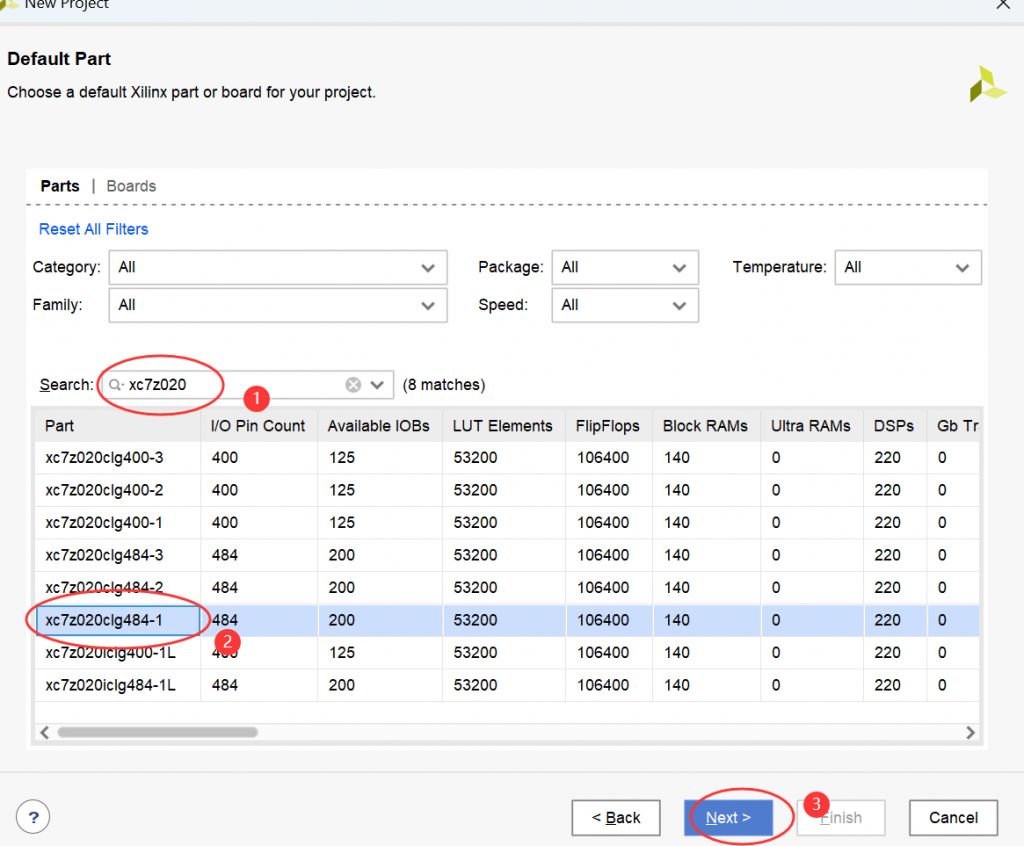

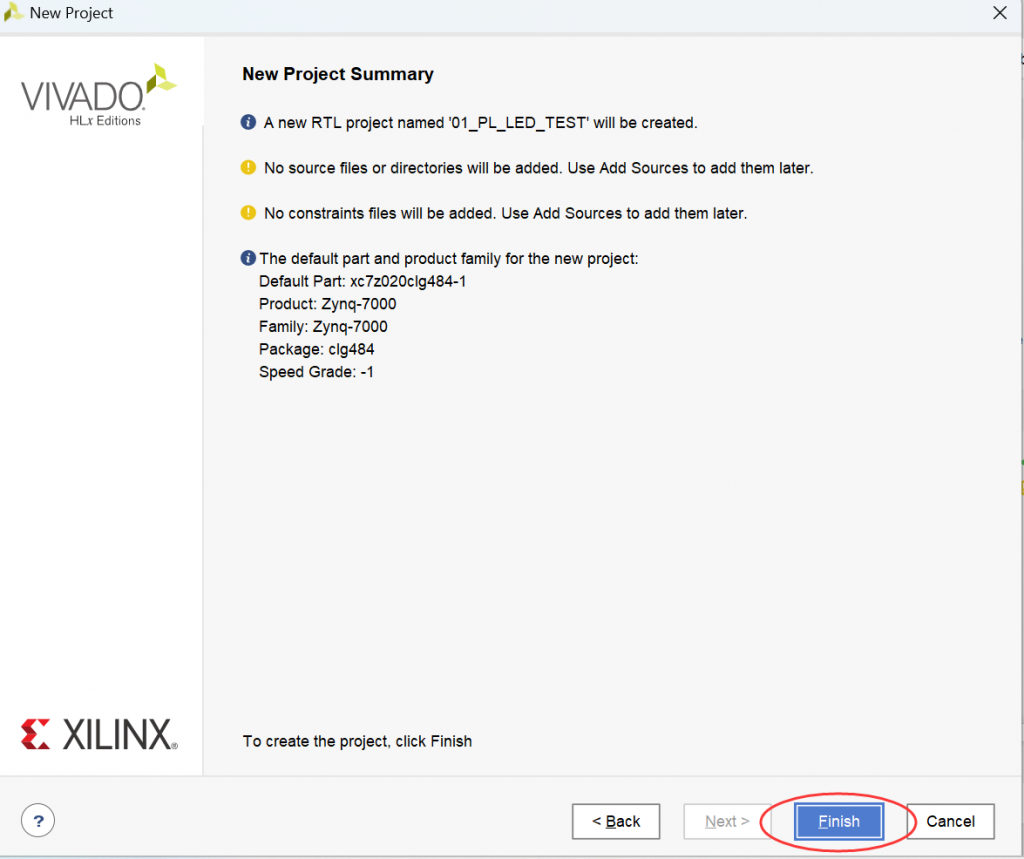

6)选择芯片型号 板子的芯片型号为 XC7Z020 封装是CLG484 所以型号我们选择 xc7z020clg484-1

7)确认所选信息 点击“Finish”,完成vivado的工程创建

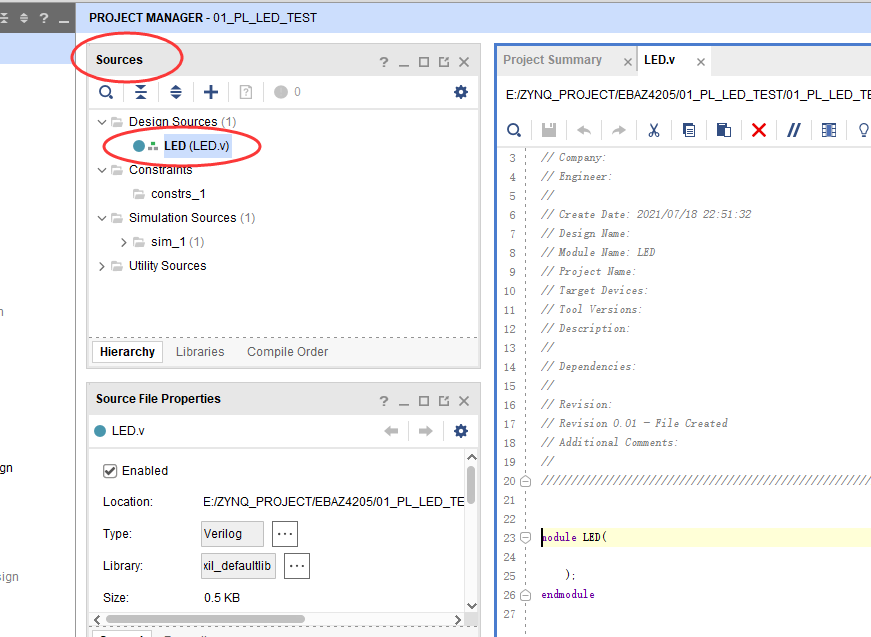

二、添加VERILOG 文件

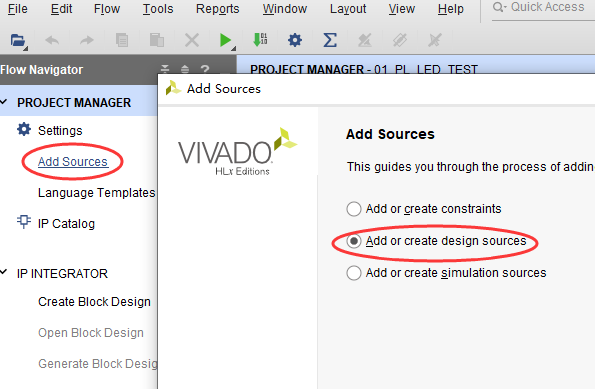

1)在主界面点击左侧 Add Sources ,点击 复选框的Add or create design sources 选项 并点击NEXT

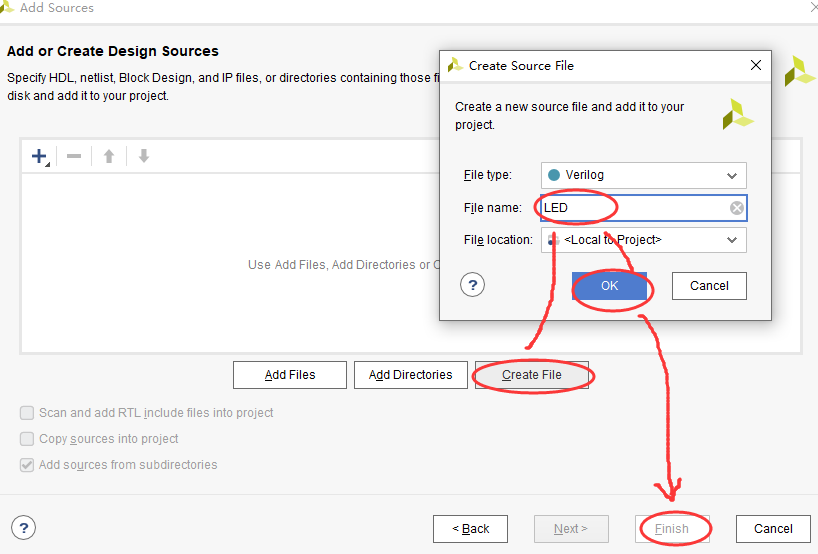

2)在出现的Add Sources 中 选择创建新文件 Create FILE 如下图所示,并在弹出的窗口中 选择类别为Verilog ,在FILE name中填写文件的名称,这里用LED 代替,点击OK 并点击FINISH

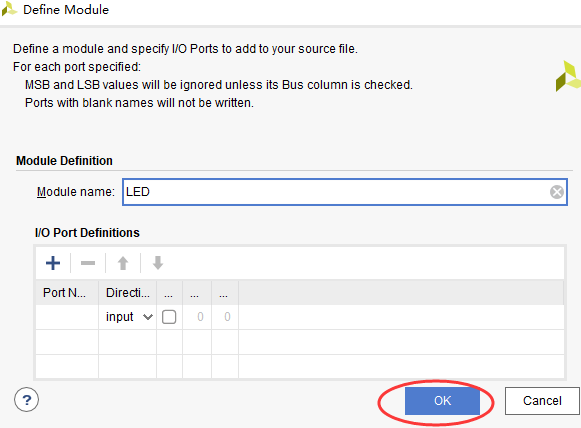

3)在跳出的窗口中可以填写模块的输入输出信号,由于这部分工作在代码中可以完成,所以这里直接点OK 完成VERILOG 文件的创建

三、编写VERILOG的代码

1)双击打开刚才创建的LED.V文件 并在里面写入LED的代码

`timescale 1ns / 1ps

module LED(

input clk,

output led

);

parameter T1MS = 26'd50_000_000 ; //50M晶振时钟

reg [25:0]time_count=26'd0;//时钟计数器

reg led_r=1'b0;

always@(posedge clk)

if(time_count>=T1MS)begin

time_count<=26'd0;

led_r<=~led_r;

end

else time_count<=time_count+1'b1;

assign led=led_r;

endmodule

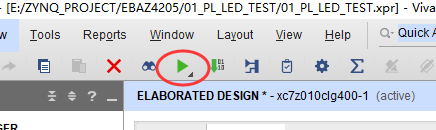

2)编写好代码后 对代码进行编译,按下绿色箭头

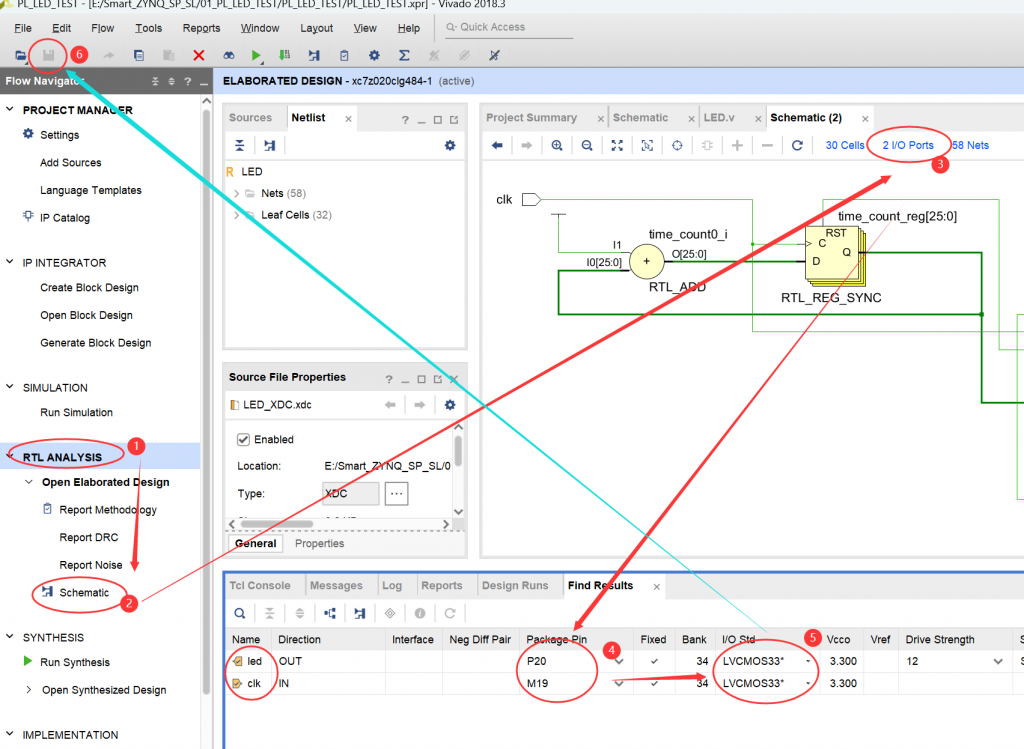

3)接下来我们要对管脚进行约束(有两种方式,一种是用图形界面的方式,一种是通过写约束文件来进行设置 ,两种方式结果相同最终都生成相同的约束文件——本文以图形界面方式进行介绍)

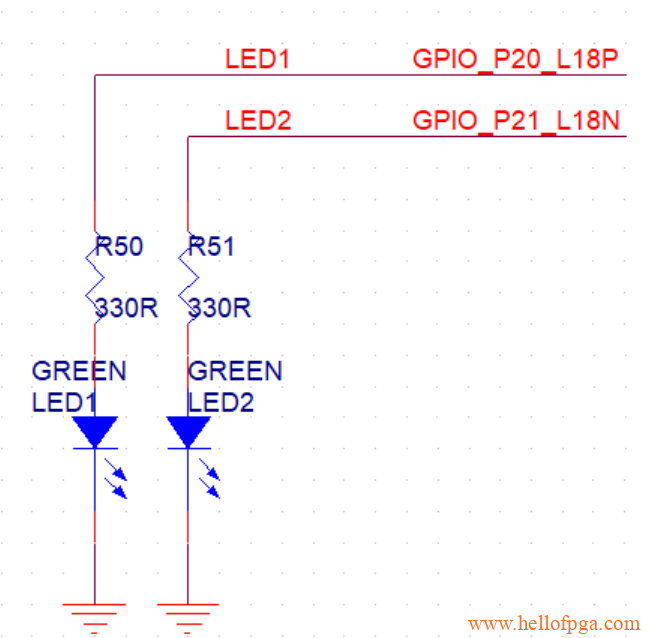

图形界面管脚设置 1)先在Package pin 中修改IO接口, 板子上CLK接到芯片的M19脚, LED 接到芯片的P20脚 2)在蓝色窗口的右侧I/O std 填入 IO接口和管脚电气属性,这里是3.3V 选择LVCOMS3V3

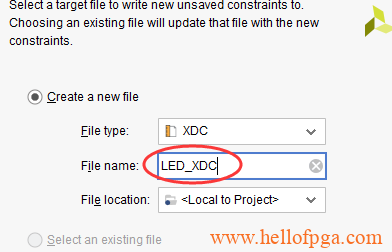

4)选择保存,第一次保存时会要求填入约束文件的名称,管脚定义的信息会被保存到约束文件中

5)之后工程里会多一个约束文件,约束文件里会多出我们刚才添加的管脚定义(我们也可以直接添加和修改约束文件来实现管脚的定义,这样就不用上一步的操作了)

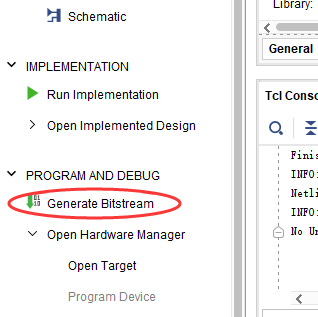

6)保存之后 点击 Generate Bitstream 进行综合以及生成Bit 文件

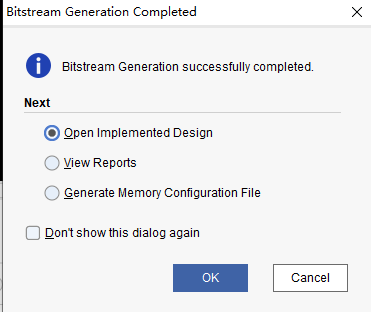

7)成功后会出现下图对话框,点OK 确认就好

四、下载调试

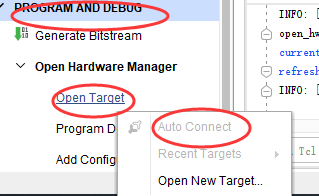

1)用TYPE C数据线将板子的JTAG口和电脑连接,给板子通上电源后,点击 PROGRAM AND DEBUG 中的OPEN TARGET 下的Auto Connect 来连接板子

如果连接正常会在右侧 硬件栏中显示设备,如下图所示

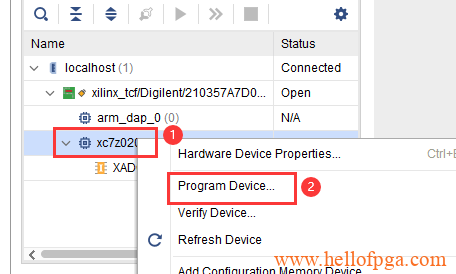

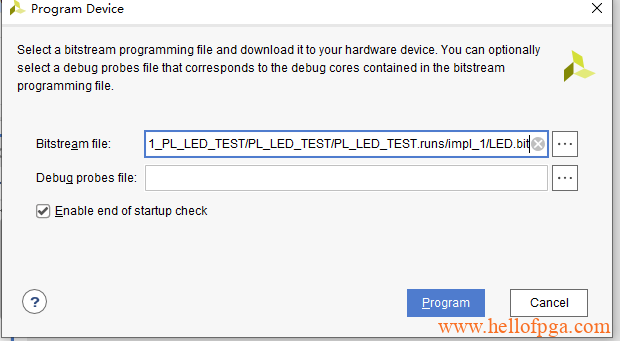

2)接下来下载bit文件,右键设备 然后选择 Program Device

3)默认会出现生成的BIT文件,如果没有的话需要手动添加路径 ,点击PROGRAM 下载

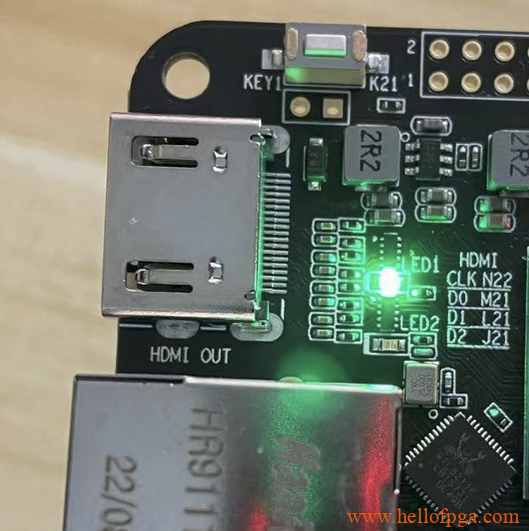

4)下载之后,板子就按照我们的代码开始跑了 P20的LED 灯开始以1S的时间间隔开始闪烁(同时程序下载完成后 仅挨芯片的DONE 灯也亮起,代表芯片正常工作了)

以上就是一个工程的完成实现过程。(关于LED代码的解读可以看实验二中的内容)

本章节的工程:

- 本文的完整工程下载:01_PL_LED_TEST_XC7Z020

- VIVADO的版本:2018.3

- 工程适用主板: Smart ZYNQ (SP / SP2 / SL) (不适用于Smart ZYNQ 标准版 )