包含Smart Zynq (SL 版)的原理图,注意事项,以及后续更新的转接板的原理图等一些资料

首先感谢各位的关注和支持,有任何问题可以直接在本站留言,或者在淘宝搜索店铺:杭海电子科技 。

另外备注 本页是 Smart ZYNQ SL版本的资料,如果是Smart ZYNQ 标准版 或者SP版 SP2版 的主板 请看对应的内容。

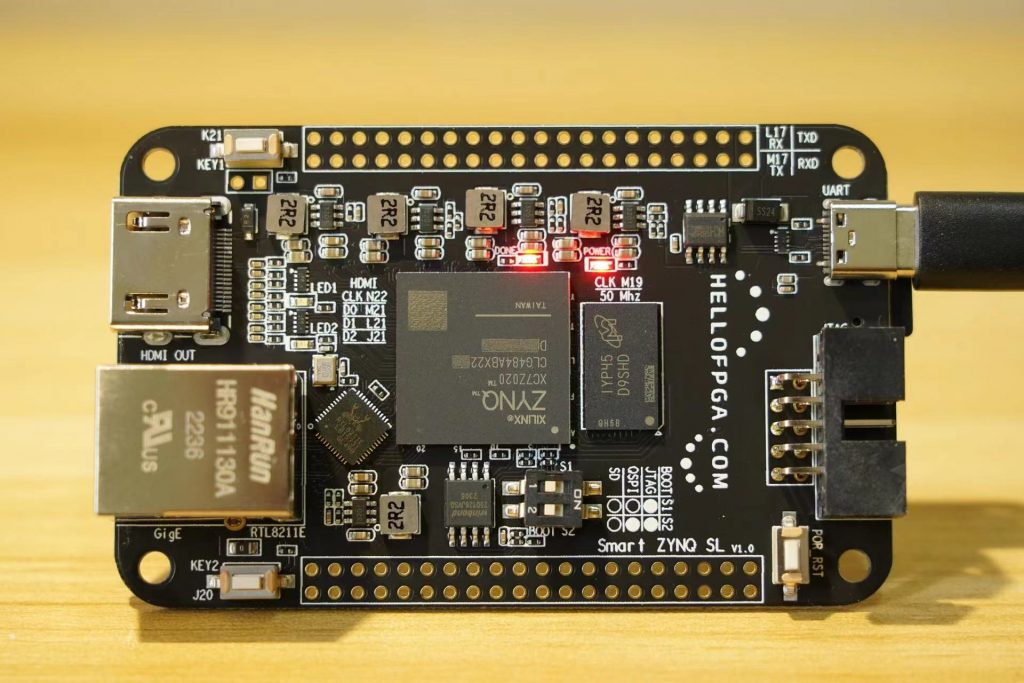

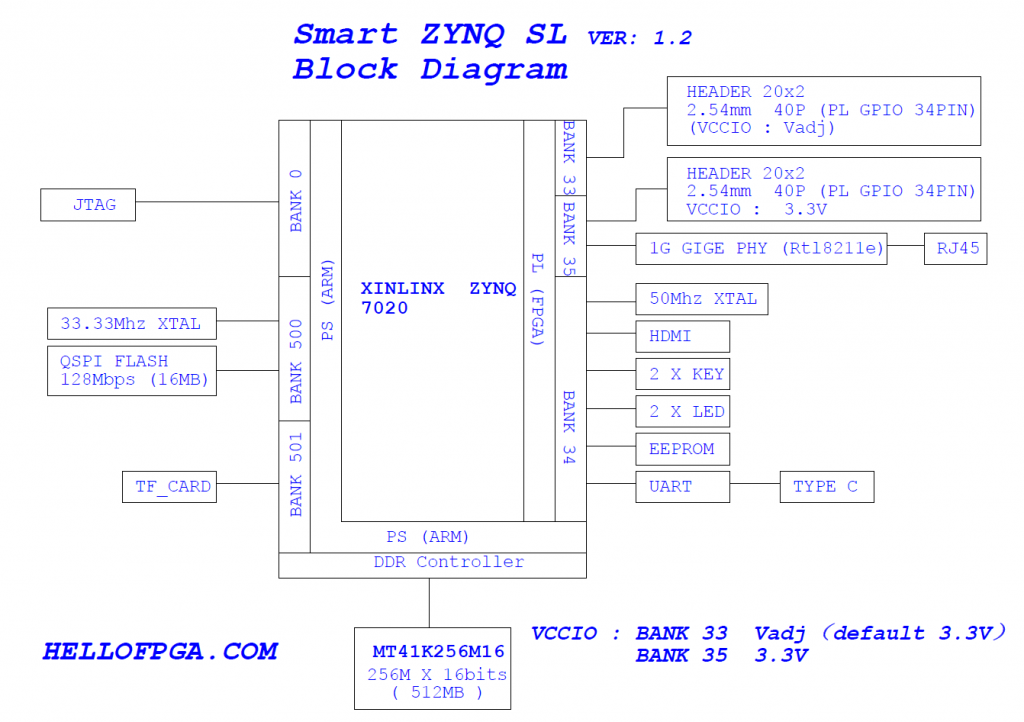

Smart ZYNQ SL 主板资源

- 主芯片:ZYNQ XC7Z020-CLG484

- 主板层数:8层(沉金工艺)

- DDR内存 : 256M x 16bit (512MB)

- FLASH : 128Mbits (16MB)(接PS端用于系统启动)

- EEPROM: 24C02 2kbits

- TF插槽:microSD 插槽 (TF卡插槽,可用于系统启动)

- 时钟 : PS端:33.33M有源晶振 , PL端:50M有源晶振

- 网络: 一路千兆以太网RTL8211E (接PL端,PS也可使用)

- HDMI: 一路HDMI 接口(IO模拟)

- 串口: 带一路USB-UART(连接至PL端,PS端也可使用

- 按键: 2个按键(PL端) + 1个POR硬件复位按键

- LED: 2个可编程LED(PL端 )+Done 指示LED + 电源指示LED

- 拨码开关:双路拨码开关(负责启动方式选择)

- 逻辑IO: 总共引出68个FPGA_IO,所有引出的管脚均以差分线方式两两引出(差分线内等长)(全都由PL端引出,PS可通过EMIO方式映射)

- 引出的GPIO中 其中一边的bank电压单独可调(通过调整一个0805封装电阻)

- 电源:主板可以通过TYPE C口(JTAG或 USB SLAVE)进行供电,或者用转接板通过排针给主板的VCC脚供上5V电源

- 板子不带下载器需要外接XILINX 下载器。

SP 和SL 版 相同资源的程序 是可以完全兼容的,管脚和GPIO的线序也完全一致,除USB HOST ,USB SLAVE 以及 板载 LCD 等SL版没有的功能外 其余资料相通

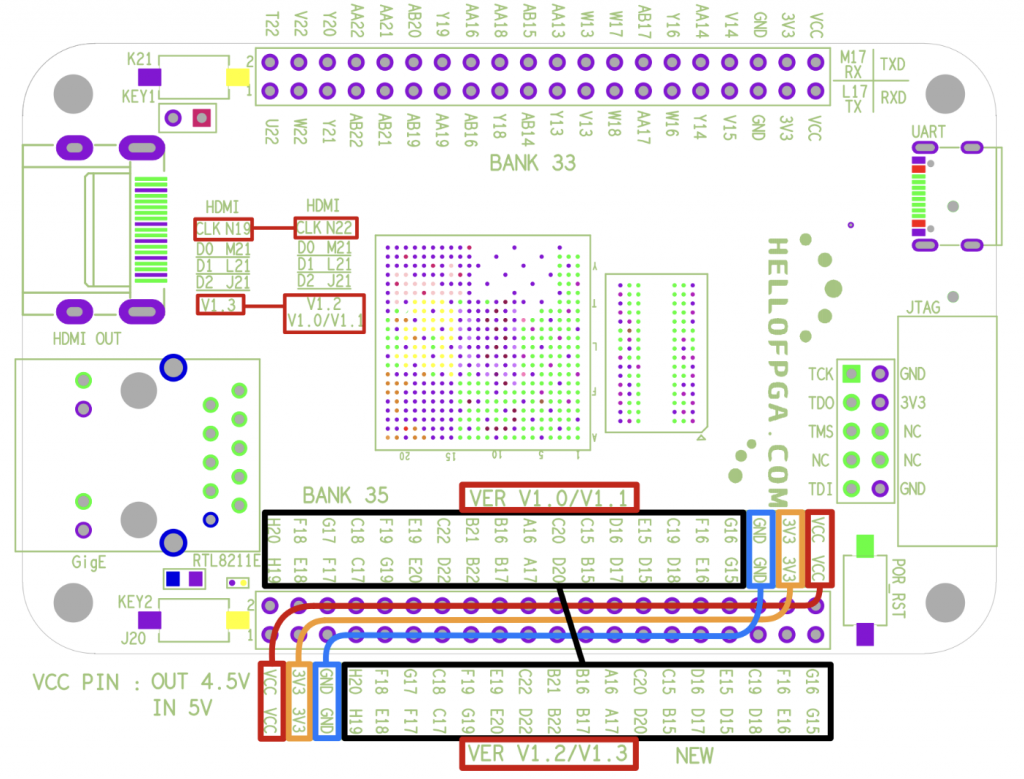

V1.3/V1.2版本硬件调整说明:

- 24年10月之后出货的硬件版本将陆续调整为 V1.3,版本信息请见主板丝印(靠近POR按键处)

- 调整了一边排针的电源位置 : V1.3/V1.2较V1.1/V1.0版调整了一边排针的电源位置(调整后的主板左右两边的排针都可以适配相同的外设模块)(1.3/1.2引脚不再兼容1.0/1.1)

- 调整了电源芯片:V1.3/V1.2版较V1.1/V1.0版电源供电芯片型号由TI家的TPS563201,更换为TPS563210A(带PG信号)

- HDMI部分CLK信号引脚调整:V1.3版在V1.2版基础上(V1.2/V1.1/V1.0版相同)调整了HDMI的CLK引脚为SRCC时钟引脚,从N22脚改为N19脚(为了适配少数仅支持SRCC作为HDMI时钟的第三方HDMI IP核) 增加了HDMI I2C信号(预留)以及HDMI_RX_HPD信号(预留)

硬件版本改变如下列框图所示:

V1.3版主板原理图如下 (同样适用于V1.2,V1.0,V1.1主板,区别已在原理图中标注出)(如需要V1.2,V1.1单独的原理图可在评论区中找到)(最新更新 2024年10月3日)

尺寸图

板子上排针的 引脚长度报告:(备注 差分线 组内都做了等长,组外没有做等长,如果设计底板过程中对等长有要求,请参考下列长度报告)

板子上所有功能IC 的数据手册:

注意事项

- 关于BANK33的电压, BANK 33电压可以通过调整背面两颗0805大小的电阻(板子上丝印标注为RA RB)来实现电压的调整(出厂默认是3.3V)

- Smart ZYNQ SP2板子上的USB SLAVE 和 USB HOST 是共用ZYNQ的USB资源的,所以同一时间只能使用一种功能(USB HOST 和USB SLAVE 不可同时外接设备,另当USB 功能作为HOST使用时如需要用USB SLAVE口为板子进行供电请接USB适配器而不是接电脑)。

- 板子上的两个TYPE C接口都可为板子进行供电,板子排针上的VCC口也可以外接5V 为板子进行供电,USB和排针外接供电互不冲突(USB有二极管作电源防倒流保护),另外备注:部分台式机前面的USB口线损较大,如用台式机的USB供电出现不稳定的情况,请尝试连接台式机背后的USB口。

- 部分笔记本和电脑的USB口输出电流限制在5V 500ma,这对于主板的运行已经足够了, 但如果主板需要外接模块,或者USB口外接功率较大的USB设备导致工作不稳定时,可以通过排针或者外接转接板单独为板子提供5V电源(排针的VCC脚)。另外外接USB设备或者模块时,建议先在断电情况下接好设备或模块,再对主板进行上电。

- 排针上的VCC口可作为电源输入,也可作为电源输出。作为输入时:可外接5V电源(即通过转接板,或者底板为板子供电,如用杜邦线供电效果会差一些)。作为输出时:(没有外接5V电源,仅通过USB供电时)可以输出4.5-4.7V的电压(即主板为转接板供电)。

- 板子上的 POR RST 是整个硬件的复位按钮 (优先级高于任何程序,只要此按键按下整个系统将根据BOOT启动方式重新启动)。

随板预下载的演示程序介绍 (boot模式选择 QSPI FLASH再上电)

- HDMI输出720p的 测试彩色条纹

- UART以一秒钟为间隔发送 “hello world”

- LED灯在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起)

可供测试的 TF固件 (测试固件现已支持 V1.0 -V1.3的所有版本Smart ZYNQ)

(使用方法:将文件下载并解压缩,将内容复制到FAT32格式的TF卡的根目录,并插入到主板上,拨码开关设置成SD启动,并按下板子上的POR复位键盘)

一、全功能测试固件一 (裸奔版 GPIO+ UART + KEY + LED 测试)

- 所有的GPIO (排针输出端)每一秒钟翻转一次电平状态(即一直不停的输出高低电平)

- HDMI输出720p的 测试彩色条纹

- UART以一秒钟为间隔发送 “hello world”

- LED灯在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起)

- 测试固件下载: Smart_ZYNQ_SP2_SL_ALL_TEST_20240916

二、全功能测试固件二(LINUX版 GPIO+ UART + KEY + LED +NET 测试)

- ALL_GPIO:(排针输出端)每一秒钟翻转一次电平状态(即一直不停的输出高低电平)

- HDMI : 输出720p的 测试彩色条纹

- UART: 输出 LINUX命令行(可用putty 等工具查看)

- LED灯:在上电后以流水灯的方式 来回点亮 (一旦按下KEY1 KEY2 任意按键,则流水灯停止,程序切换到对应按键方向的灯亮起)

- NET: 用网线连接路由器,可以在串口命令行中看到网络已连接的提示, 这个时候可以尝试ping路由器和其他网络设备。

- 测试固件下载:Smart_ZYNQ_SP2_LINUX_ALL_TEST_20240906

已整理的一些图文例程(持续更新中)

备注 本站所有的资料都是基于VIVADO2018.3版本的,如果不熟悉开发过程,版本尽量保持一致基于Smart ZYNQ (SP SP2 SL) 的FPGA实验

主板相关

基于Smart ZYNQ (SP SP2 SL) 的FPGA实验

- 当遇到ZYNQ ,SDK debug失败报错的解决方法

- ZYNQ板PL部分程序添加复位信号的几种办法

- Vivado 2018.3 下载及安装

- Verilog 快速上手笔记

- Vivado 2019.2 以上带 vitis 版本的简单教程演示 (本文大多数例子都是基于2018.3创建的,所以本章节选看)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验一 用ZYNQ的PL资源点亮一个LED (完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验二 用ZYNQ的PL(FPGA)设计流水灯

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验三 PL部分按键功能演示(IO输入功能)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验四 Vivado自带的仿真功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验五 FPGA 硬件调试 ILA功能的演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验六 FPGA的 VIO在线调试功能测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验七 FPGA资源的PWM演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验八 FPGA片内资源MMCM/PLL 时钟模块的测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验九 FPGA片内资源 BLOCK RAM IP核的使用

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十 在PL端调用片内XADC资源来读取 ADC对应管脚的电平电压

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十一 基于双路高速ADC模块的信号采集实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十二 基于ZYNQ PL资源的HDMI功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的FPGA实验十三 基于PL的RGB888屏幕调试 ( 5INCH 800X480屏)

- 纯FPGA程序固化啊部分可以参看PS的实验:

- PS端为PL端提供时钟部分可以参看PS的试验:

- PL端与PS端交互的部分可以参看下面三个PS实验:

基于Smart ZYNQ (SP SP2 SL) 的PS实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验一 GPIO之用EMIO方式点亮LED(完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二 GPIO之用AXI-GPIO方式点亮LED (完整图文)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验三 GPIO之按键功能演示(EMIO方式)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验四 外部中断实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验五 定时器中断实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验六 将程序固化至QSPI FLASH(FLASH启动)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验六 (补充) 纯FPGA程序 固化至QSPI FLASH

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验七 将程序放置在TF卡并进行TF卡启动演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验八 UART功能演示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验九 QSPI FLASH读写测试

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十 千兆网络初测(基于EMIO)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十二 ZYNQ PS 端的双核AMP实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十三 PS与PL数据交互之 PS访问 PL端的reg 寄存器

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十四 PS与PL数据交互之 PL(FPGA)读写 PS端DDR的实验

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十五 PS与PL数据交互之 PS访问 PL端的BRAM资源实现PS与PL数据交互

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十六 通过PS部分来为PL逻辑提供时钟(做工程时的常用方法)

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十七 调用片内XADC资源 来实时读取芯片的电源和温度等信息

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验十九 用VDMA模块来缓存图像并在HDMI上显示(一)PS端彩条纹的显示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十 用VDMA模块来缓存图像并在HDMI上显示(二)显示TF卡上的BMP格式图片

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十一 5寸RGB屏实验:用VDMA模块来缓存图像并在LCD上显示(一)PS端彩条纹的显示

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十二 5寸RGB屏实验: 用VDMA模块来缓存图像并在LCD上显示(二)显示TF卡上的BMP格式图片

- 基于Smart ZYNQ (SP/SP2/SL 版) 的PS实验二十三 5寸RGB屏实验: 电容触摸部分DEMO

基于Smart ZYNQ (SP SP2 SL) 的LVGL实验

基于本站 ZYNQ 主板的 LVGL(V8.3.10版本)的手把手移植教程(VDMA+DMA方式)

基于Smart Zynq 的Petalinux部分图文教程

- Petalinux开发准备工作:

- 基于Smart Zynq 的Petalinux开发:

- 基于Smart Zynq 的Petalinux开发 章节一 Vivado 基础硬件工程搭建

- 基于Smart Zynq 的Petalinux开发 章节二 在 Ubuntu 上完成 Petalinux 的工程创建及编译全过程(TF卡启动)

- 基于Smart Zynq 的Petalinux开发 章节三 创建可用于Petalinux 系统启动的SD卡(包含boot和rootfs分区)

- 基于Smart Zynq 的Petalinux开发 章节四 启动验证

- 基于Smart Zynq 的Petalinux开发 章节五 通过SSH远程登录petalinux系统

- 基于Smart Zynq 的Petalinux开发 章节六 Windows 通过 SCP 命令 远程传输文件给petalinux 系统

- 基于Smart Zynq 的Petalinux开发 章节七 GPIO的输入输出实验

- 基于Smart Zynq 的Petalinux开发 章节八 GPIO的输入输出实验二——通过编写应用程序来控制

- 基于Smart Zynq 的Petalinux开发 章节九 USB HOST实验 (Smart ZYNQ SL不适用)

- 基于Smart Zynq 的Petalinux开发 章节十 从QSPI FLASH 启动LINUX镜像

下面是PYNQ 部分的图文教程资料(已跑通,镜像在章节三)

- PYNQ 开发 章节一 开发移植环境的部署

- PYNQ 开发 章节二 Vivado 硬件工程搭建 (Smart Zynq SP & SL版)

- PYNQ 开发 章节三 PYNQ镜像构建 (Smart Zynq SP & SL版) (含可供测试的镜像链接)

备注 PYNQ部分仍然还在测试中,不一定完善,感兴趣的大家自行测试 2023年8月21日

Xillinux 图形化操作系统 (Smart ZYNQ SL主板因没有USB不能进入桌面系统,但可运行除桌面系统外的有限的功能,或者通过第十四章节的内容远程访问桌面系统容)

Xillinux 是Xillybus 为Zynq 发行的Linux,现已官方适配支持Smart ZYNQ SP主板,Smart ZYNQ SL主板也可以跑Xillinux 但是因为没有USB功能所以无法进入图形桌面,但可使用串口终端或者网络来进行操作)

- Xillinux 操作系统 资料整理

- Xillinux 章节一 TF卡准备工作之 镜像烧录

- Xillinux 章节二 TF卡准备工作之 demo bundle 的使用说明

- Xillinux 章节三 Xillinux 的启动验证(SL版不带USB 功能,所以暂时无法进入桌面系统, 但是可以通过第十四章节内容远程访问桌面系统)

- Xillinux 章节四 调整 file system 的大小

- Xillinux 章节五 设置自定义Ethernet MAC 地址 (选看)

- Xillinux 章节六 使用SmartZynq SP上的板载SPI LCD屏幕 (SL版不带屏幕,无法演示此功能)

- Xillinux 章节七 EEPROM 存储实验

- Xillinux 章节八 GPIO的输入输出实验

- Xillinux 章节九 通过 ssh 远程登录 Xillinux

- Xillinux 章节十 Windows 通过 SCP 命令 远程传输文件给Xillinux 系统

- Xillinux 章节十一 Xillinux 使用CIFS 挂载 Windows共享文件夹

- Xillinux 章节十二 在Xillinux 系统上搭建 CIFS服务(samba),实现与Windows 文件共享

- Xillinux 章节十三 在Xillinux 系统中自动挂载(mount) TF卡分区

- Xillinux 章节十四 在 Windows 计算机上远程显示并操作Xillinux 桌面及应用

- Xillinux 章节十五 将普通耳机连接到 digital output pin 并播放音乐

- Xillinux 章节十六 使用 Smart Zynq 从 OV7670 摄像头模块进行实时取景和视频捕捉

- Xillinux 章节十六 (补充一)在 Smart Zynq主板上通过 I2C接口对 OV7670 相机传感器的寄存器进行配置

UART串口接收数据无法进入接收中断,但其它的开发板没有这个问题,不知道怎么解决

这边uart 是emio 方式 但是应该对中断不影响才对 ,可能还是要工程上找找问题看看

Can I use PS SPI on this Smart Zynq SL board

You can use EMIO to map the SPI function of the PS to the PL terminal

Hi! Why is the voltage VCC3V3 output to pins 37 and 38 of the U12 connector? Logically, it should be VCCIO_ADJ

Because the use of 3.3V is more common, and there is a VCCADJ connector port on the board, which is close to the position of KEY1 (2P)

And even if the communication voltage outside the chip is 1.8V, the power supply voltage may still need 3.3V to provide

(因为相比于其他电压,3.3V更常使用, 而且很多芯片即使外设的通讯电压是1.8V,但是供电电压仍然可能需要3.3V来提供, 另外板子上有引出VCCADJ的电压,在按键KEY1 的位置附近)

Hello! But you have 5V_DC output to the connector. If necessary, any voltage can be made from 5V. Moreover, the board itself can also receive power from the 5V_DC line. At the same time, you have VCCADJ equal to 3.3V and does not go anywhere except U32. You could route VCCADJ to the connector instead of VCC3V3, they are the same anyway 3.3V. It is often necessary 2.5V but you don’t have them. It would be more convenient to make VCCADJ = 2.5V. Moreover, it’s better to make a jumper for switching 2.5/3.3V. And would be convenient to use a flat cable 40-cores, but for VCCADJ I will have to add a separate wire.

I understand what you’re saying. Thank you for your suggestion.

V1.1 V1.0版单独的原理图如下:

http://www.hellofpga.com/wp-content/uploads/2023/05/Smart_ZYNQ_SL_Schematic_20230510.pdf

V1.2版原理图如下:

http://www.hellofpga.com/wp-content/uploads/2023/05/Smart_ZYNQ_SL_V1D2_Schematic_20240719.pdf

HDMI热插拔电路原理图上是有问题的,按照原理图提供的电路ZYNQ可以控制HDMI插槽的HPD(热插拔检测管脚),但不能读取到插槽的HPD输入电压。

这个HPD 信号1.3版本之前没有的, 作为HDMI 输出,你持续给信号就可以了(可以不考虑HPD)

这个HPD信号在1.3版本之后增加是 为了给HDMI 输入功能做预留的(包括新增加的I2C 的两个信号)。 其实1.3版本的电路是已经具备HDMI输入功能了,后续会放出demo