因为本网站的资料大多都是基于2018.3来进行设计的,有很多vitis用户表示不知道该如何进行操作,所以本文做了一个简单的vitis使用教程,仅供大家参考。

本文以vivado 2020.2版本为例 ,其他版本自行尝试

备注:此文本中的芯片型号,DDR型号,以及LED的IO 是根据Smart ZYNQ SP以及SL主板来编写的,如果是Smart ZYNQ 标准版,或者其他板子请根据板子的内容自行修改

本演示工程通过演示PS的 EMIO LED 点灯程序,来让对vitis不太熟悉的用户也能快速上手vitis。(备注 vivado 部分和2018.3版本差别不大,可以参考2018.3部分的例程)

一、 硬件介绍

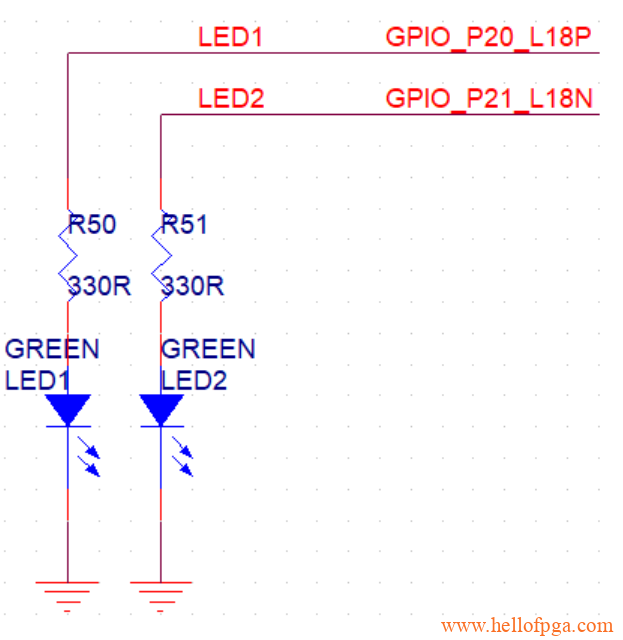

为了演示两个按键的功能,这里再引入两个指示灯,将LED的驱动脚拉高,指示灯亮,拉低指示灯熄灭,指示灯分别接在主芯片的P20和P21脚

二、创建Vivado工程

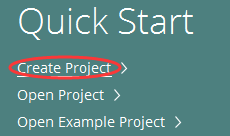

1) 具体步骤 新建一个VIVADO 工程,打开软件 选中Create Project, 如下图所示

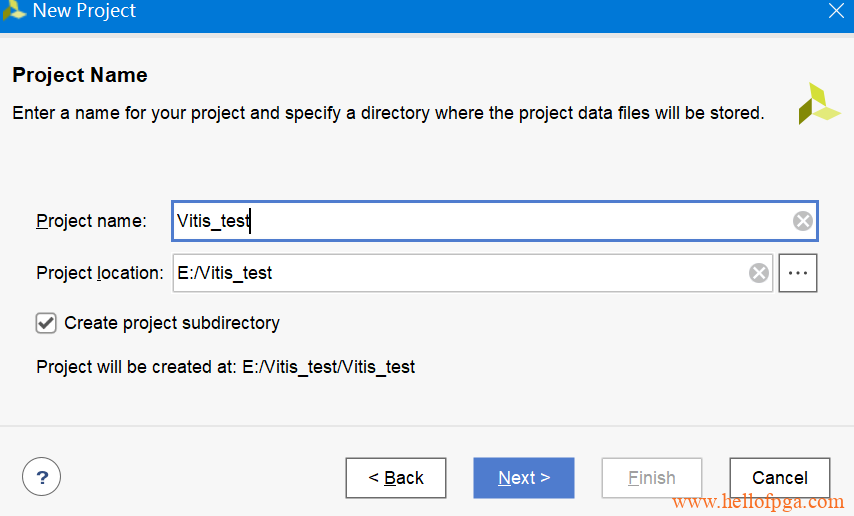

2)点击NEXT ,在出现的第二个对话框“Project name”中输入工程名;在“Project location”中选择保存路径;勾选“Create project subdirectory”,最后点击“Next” 备注,所有的路径均不能出现中文名称

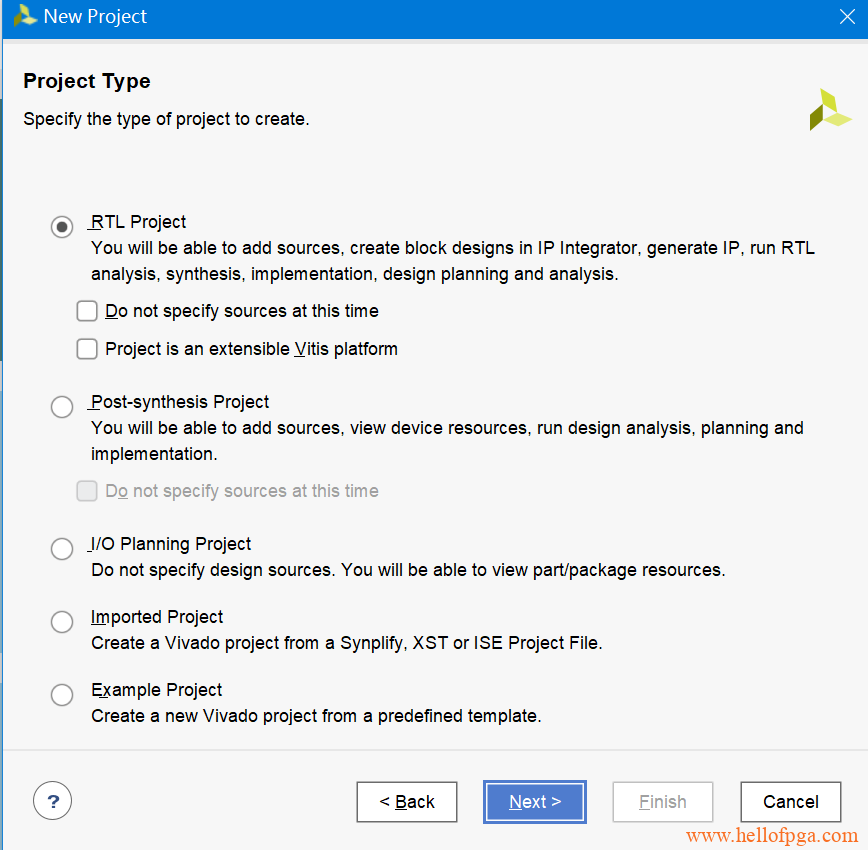

3)点击 RTL PROJECT 选项,点击NEXT

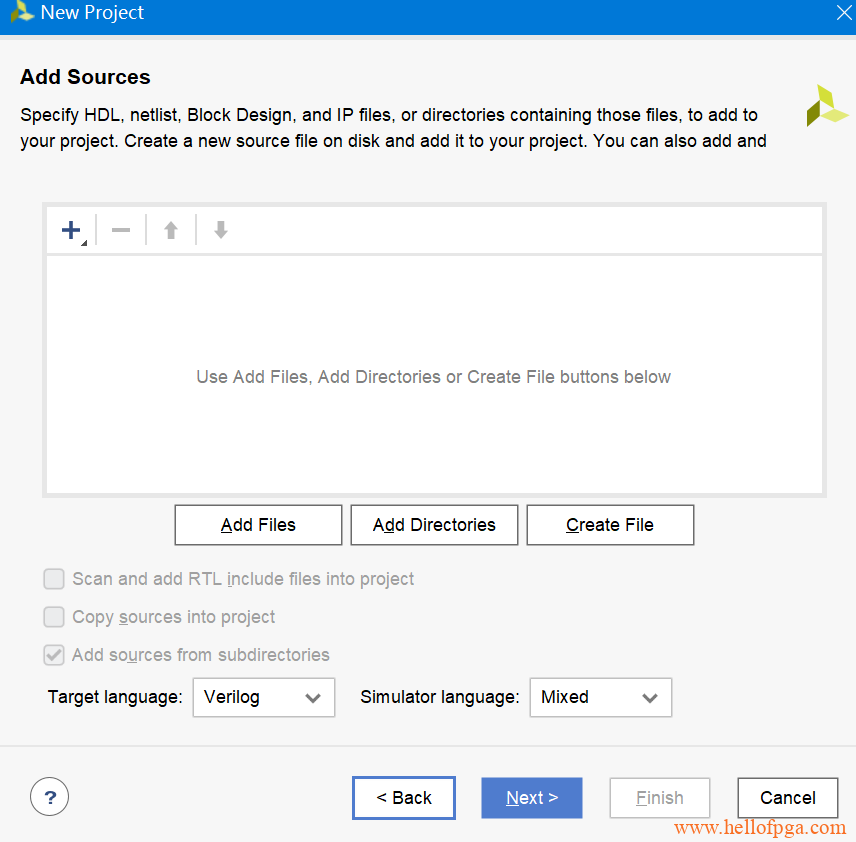

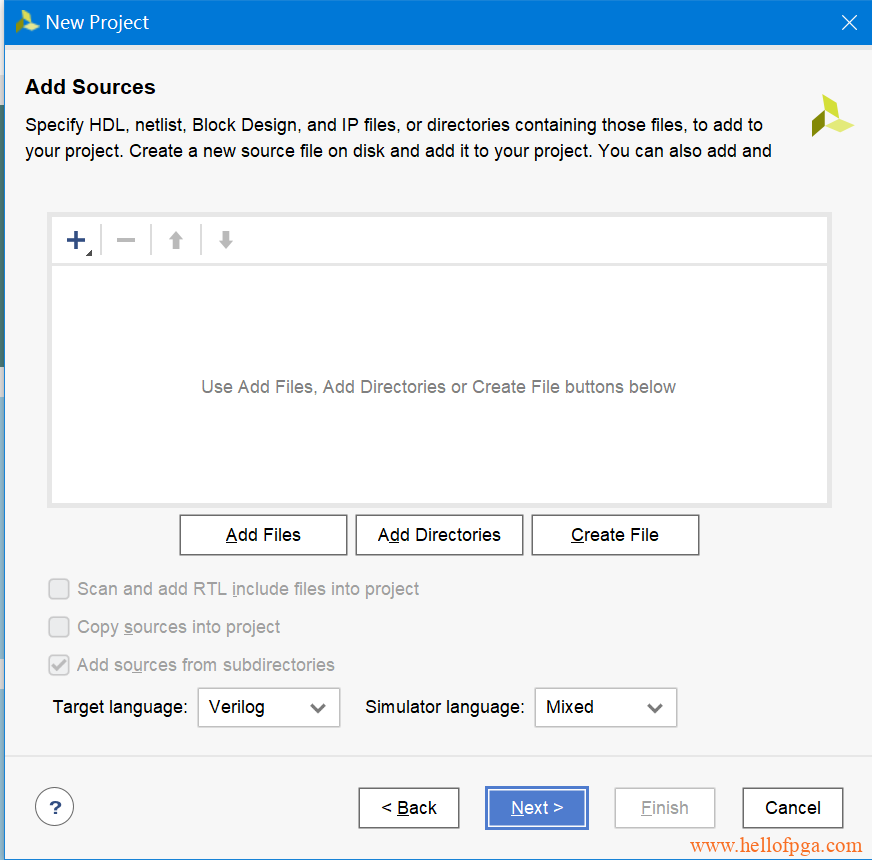

4) 第四步Add Sources 选项直接留空,NEXT

5)第五步Add Constraints 选项直接留空,NEXT

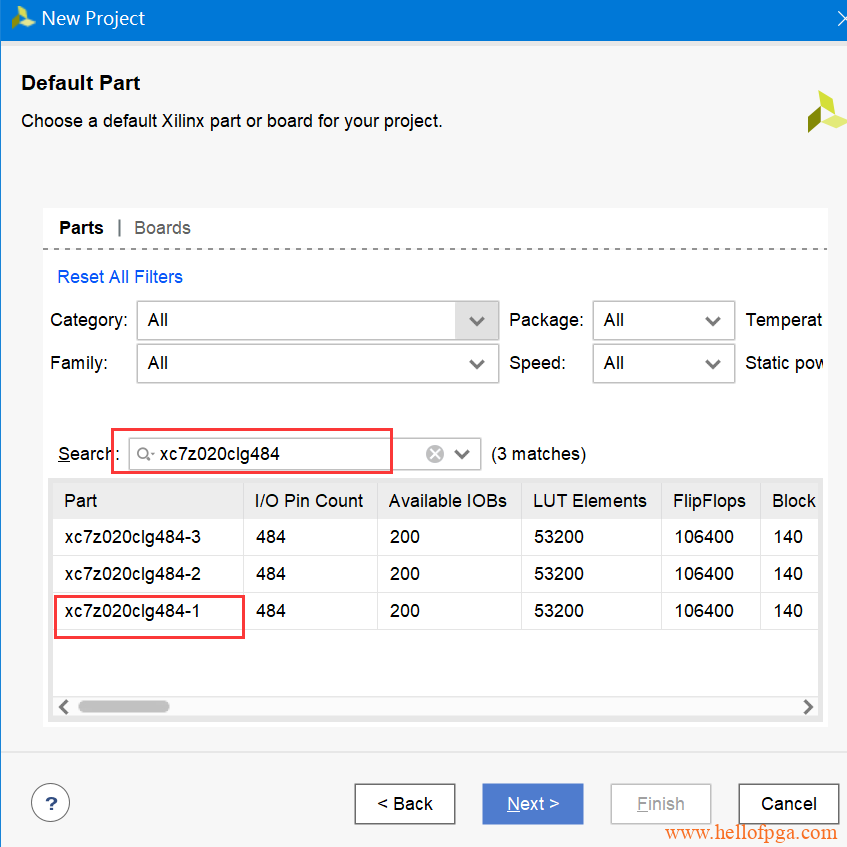

6)选择芯片型号 (xc7z020clg484-1)

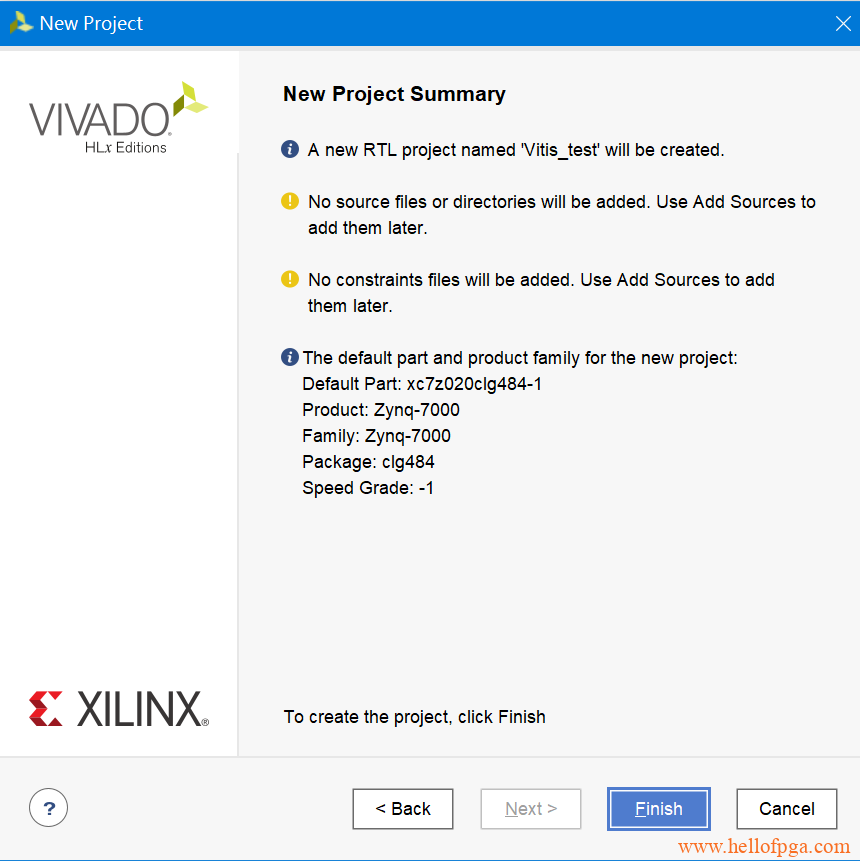

7)确认所选信息 点击“Finish”,完成vivado的工程创建

三、 创建一个BLOCK设计

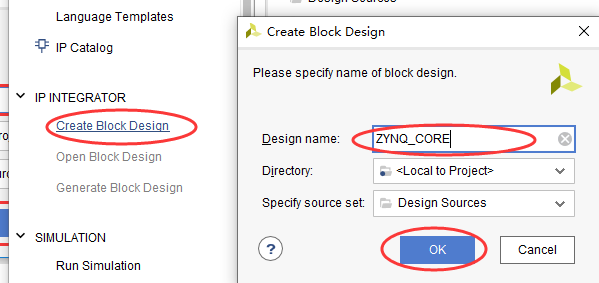

1)IP INTEGRATOR→Create Block Design,在弹出的对话框中输入设计名,最后点击“OK”,如下图所示

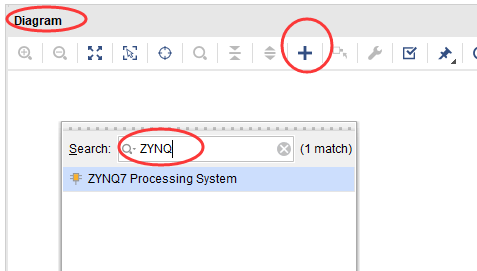

2)在右侧的窗口里 ,点击加号,在选择框里搜索ZYNQ,并找到ZYNQ7 PROCESSING SYSTEM ,双击并打开

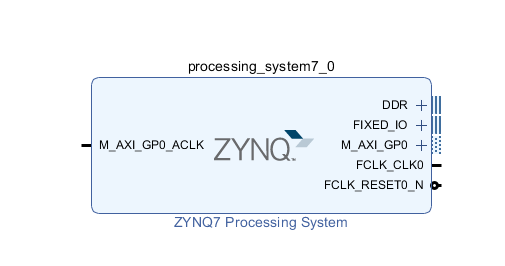

3)软件自动生成了一个 zynq的block 如下图所示,接下来要做一些相应的设置,双击下图中的ZYNQ核

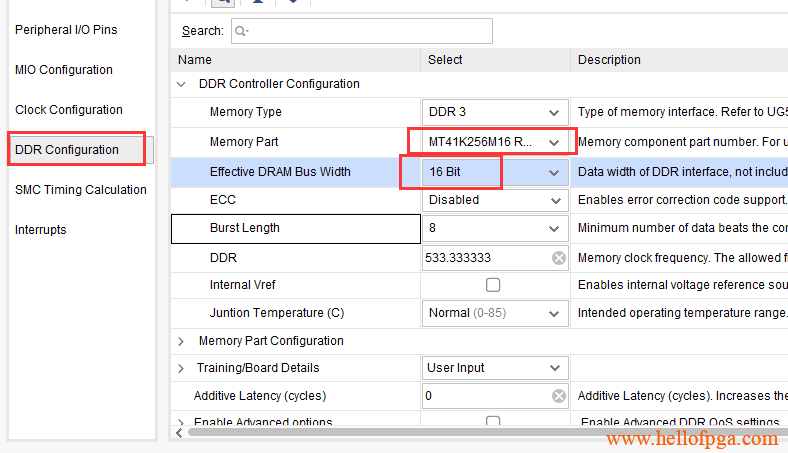

4)依次在弹窗里找到DDR Configuration→DDR Controller Configuration→DDR3,在Memory Part下拉菜单中根据自己板子上的DDR来选择相应的DDR3,本实验所用到型号:MT41K256M16RE-125,数据位宽选择16bit 最后点击“OK”,如下图所示。

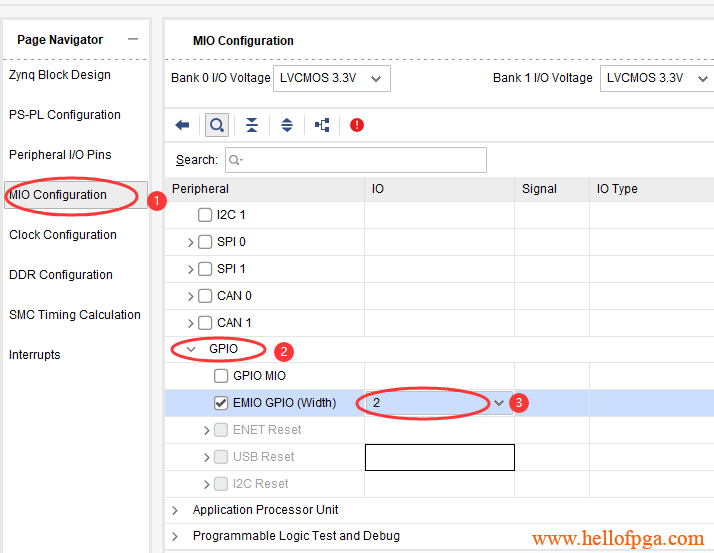

5)在PS的MIO配置选项的GPIO栏里,增加两路EMIO(因为本次测试的是两个,如果需要增加按键或者其它IO 这里可以对应的调整)

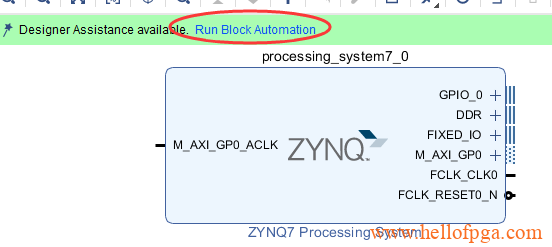

6)最后 点击“Run Block Automation”如下图所示。在弹出的选项中保持默认,点击“OK”,即可完成对ZYNQ7 Processing System的配置

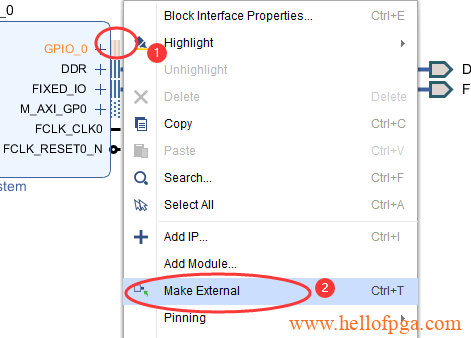

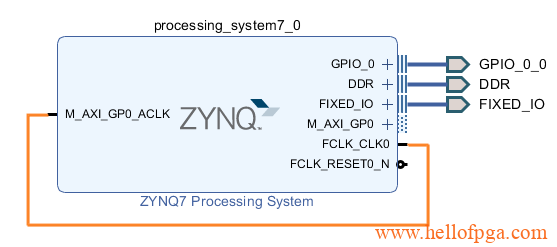

7)将刚才添加EMIO GPIO 引出 右键GPIO_0—->Make External

8)用线将M_AXI_GP0_ACLK与 FCLK_CLK0连接起来 (也可以在配置页面禁用AXI 就不需要连接了)

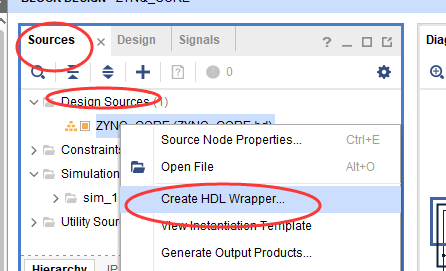

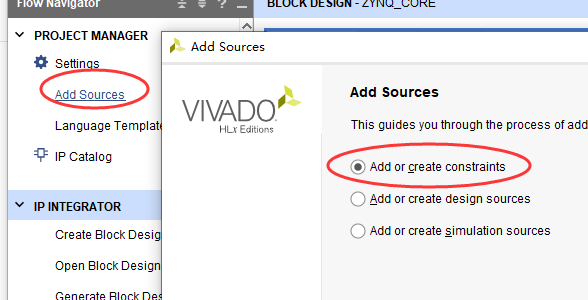

9)source→Design Source ,右键我们创建的BLOCK工程,点击create HDL wrapper如下图所示。

在弹出的对话框里保持默认

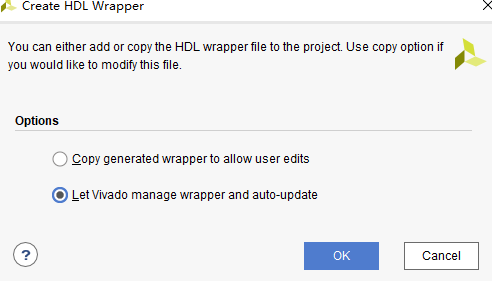

软件自动为我们生成HDL文件

四、创建约束文件,并且定义管脚

(这里使用约束方式,也可以在RTL配置界面手动选择管脚)

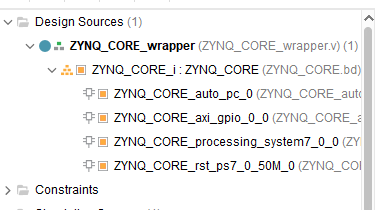

1)Add Source → Add or create constraints 点Next

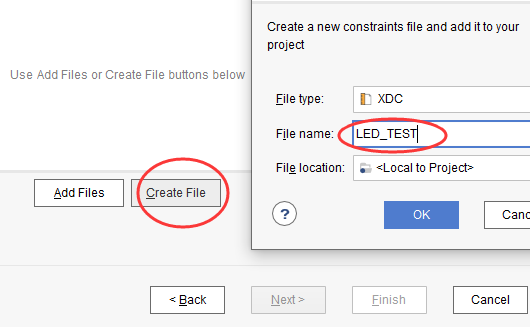

因为这个项目没有创建过约束文件 所以这里创建一个约束文件,并在File name 里设置约束文件的名称,并且点击FINISH 完成约束文件的创建

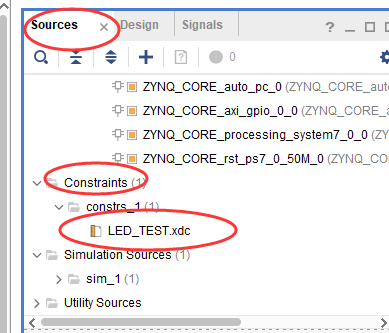

2)Sources → Constraints 里找到刚才创建的约束文件 双击并打开该XDC约束文件

在约束文件里面复制下面代码来对输出的GPIO进行管脚(所有的管脚转接板上丝印都有实际标注对应的IO)

set_property IOSTANDARD LVCMOS33 [get_ports GPIO_0_0_tri_io[0]] set_property IOSTANDARD LVCMOS33 [get_ports GPIO_0_0_tri_io[1]] set_property PACKAGE_PIN P20 [get_ports GPIO_0_0_tri_io[0]] set_property PACKAGE_PIN P21 [get_ports GPIO_0_0_tri_io[1]]

五、生成bit文件

按下绿色箭头对工程进行编译 (弹出的界面选择OK ,并且CPU CORE 选择最大即可)

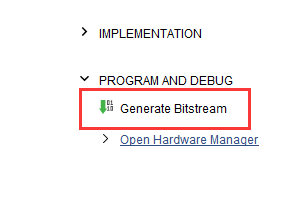

按下Generate Bitstream 完成综合以及生成bit文件

六、vitis 工程创建

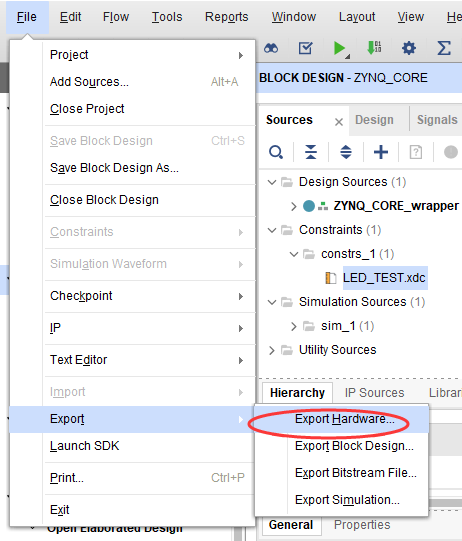

1)导出硬件

File→Export→Export hardware…

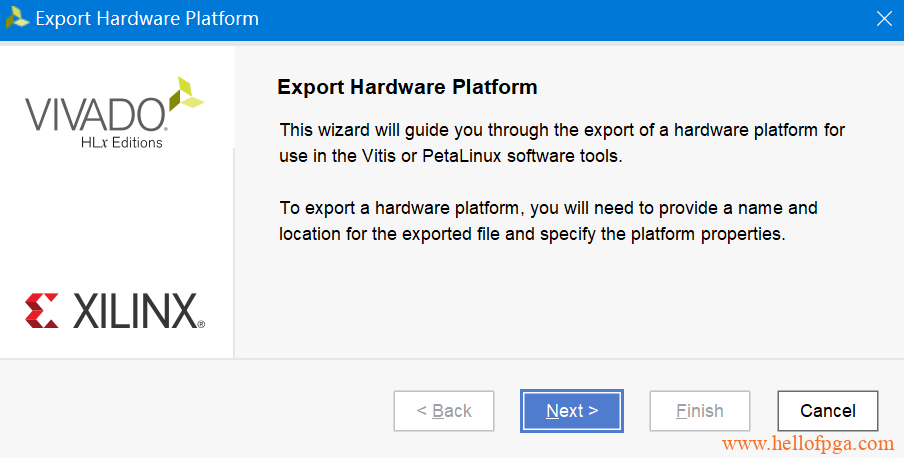

在弹出的对话框里选择Next

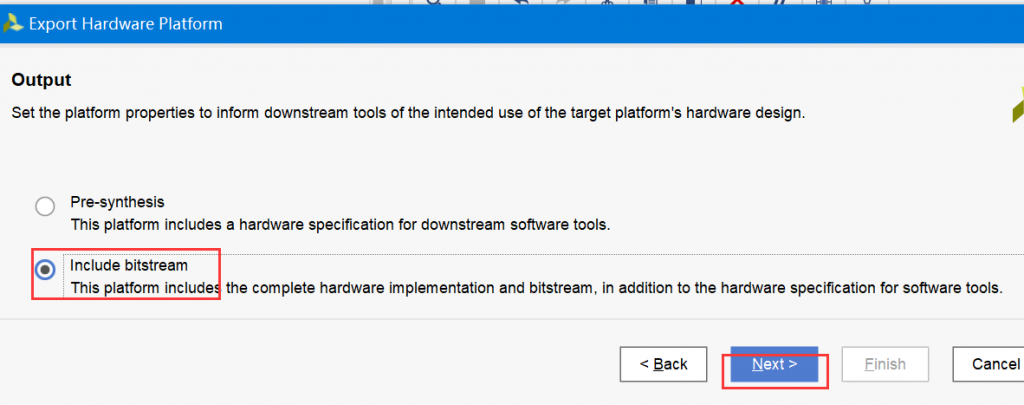

勾选 include bitstream ,再选择Next

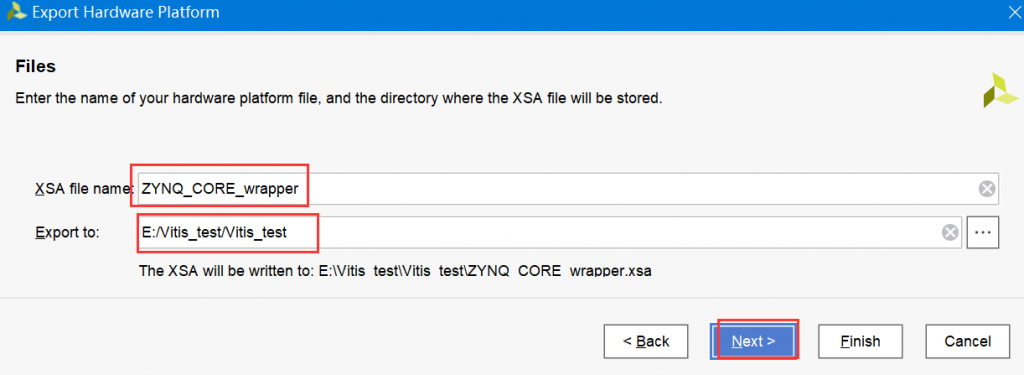

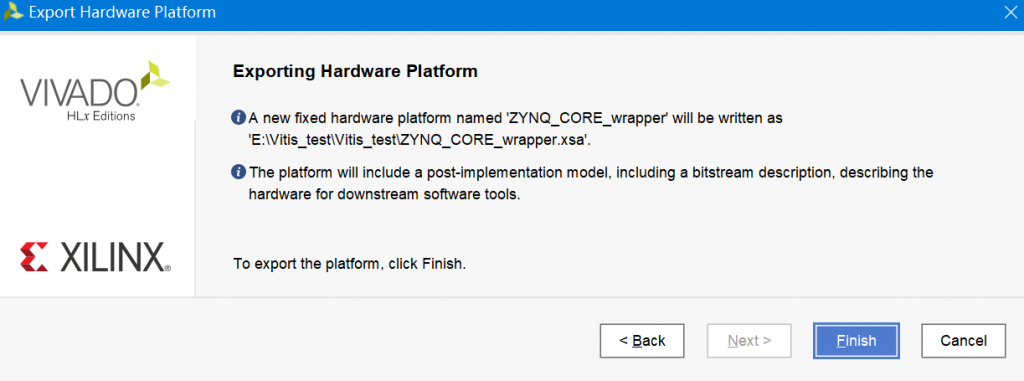

记录下导出的地址,然后选择Next

之后选择Finish

2 )启动vitis,并创建工程

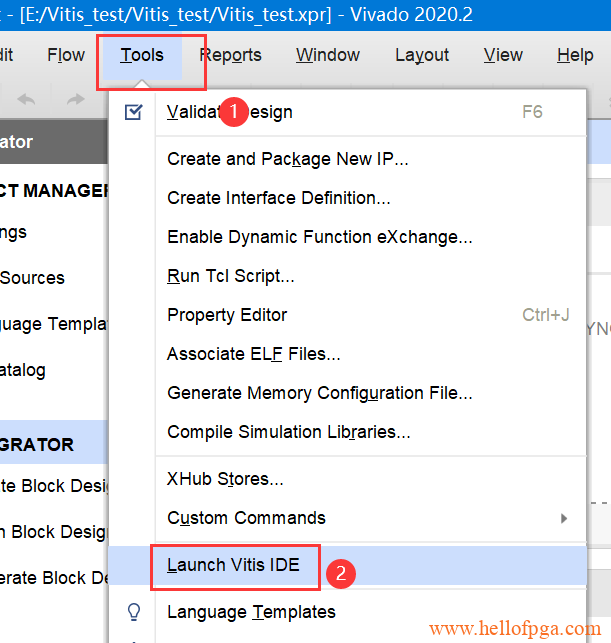

1)在vivado中启动:Tools -> launch vitis IDE

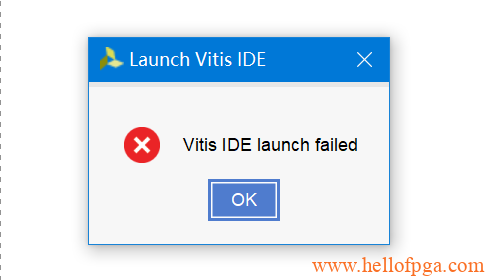

备注 如果你出现下面这样的图 ,启动失败,则说明您仅安装了 HDL 没有安装vitis 请参考CSDN这一页面增加vitis https://blog.csdn.net/tcjy1000/article/details/126567610

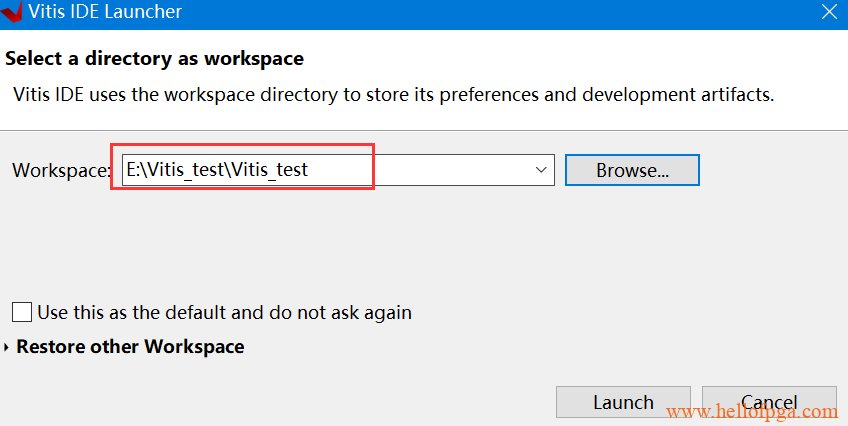

2) 启动 vitis 后,将workspace 定义在工程目录下 (备注目录名称不能带中文)

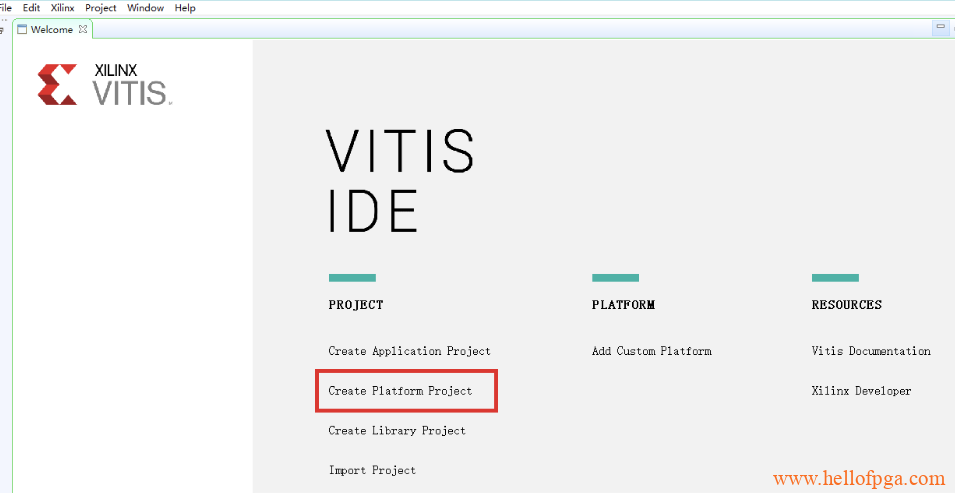

3) 点选Create Platform Project 创建工程

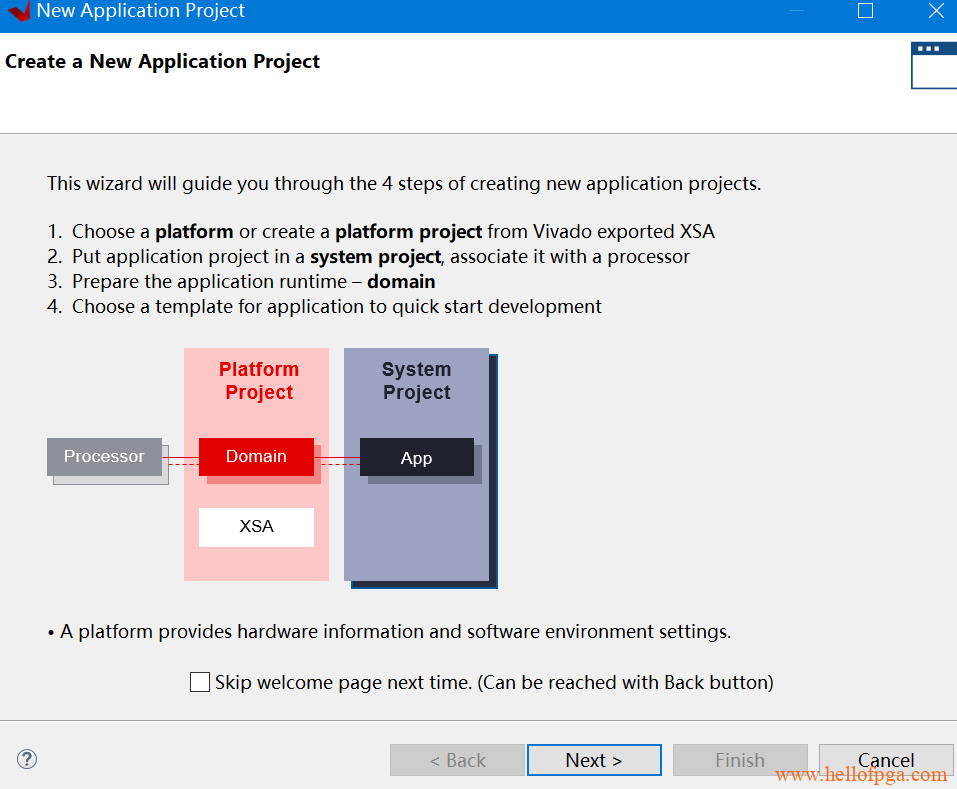

选择Next

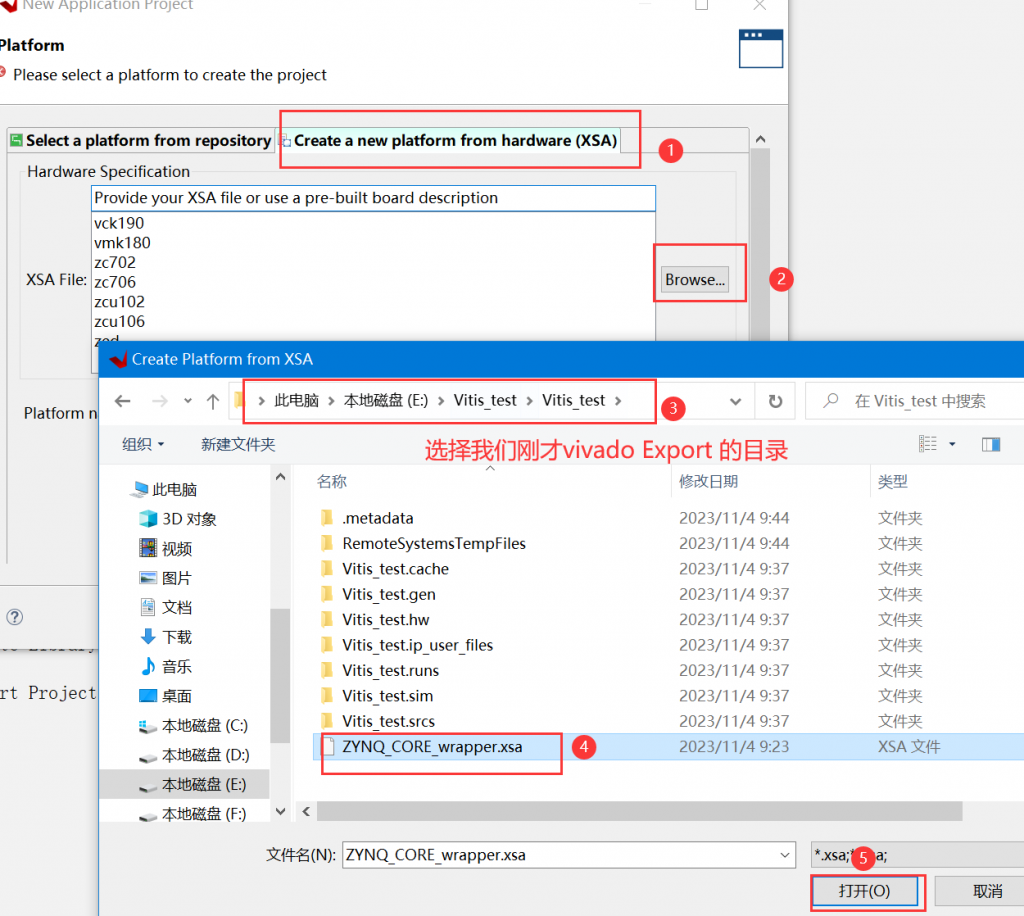

4) 选择从现有的xsa文件创建工程 ,并按下图所示,找到并加载我们的xsa文件

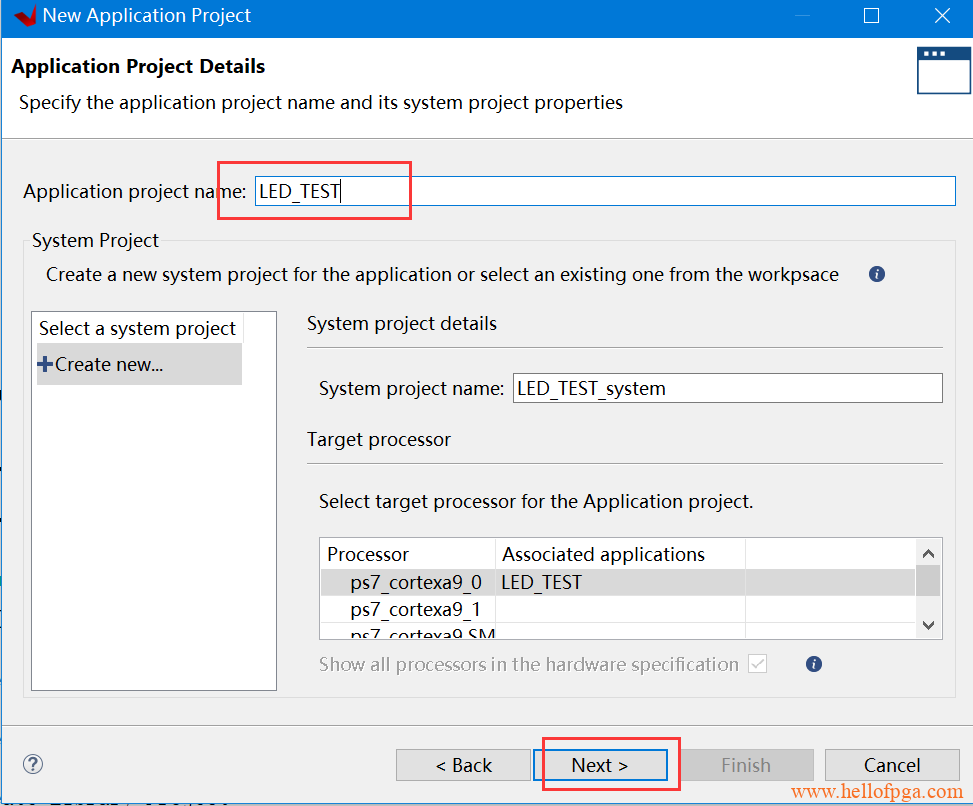

5) 这里我们定义工程名称为LED_TEST

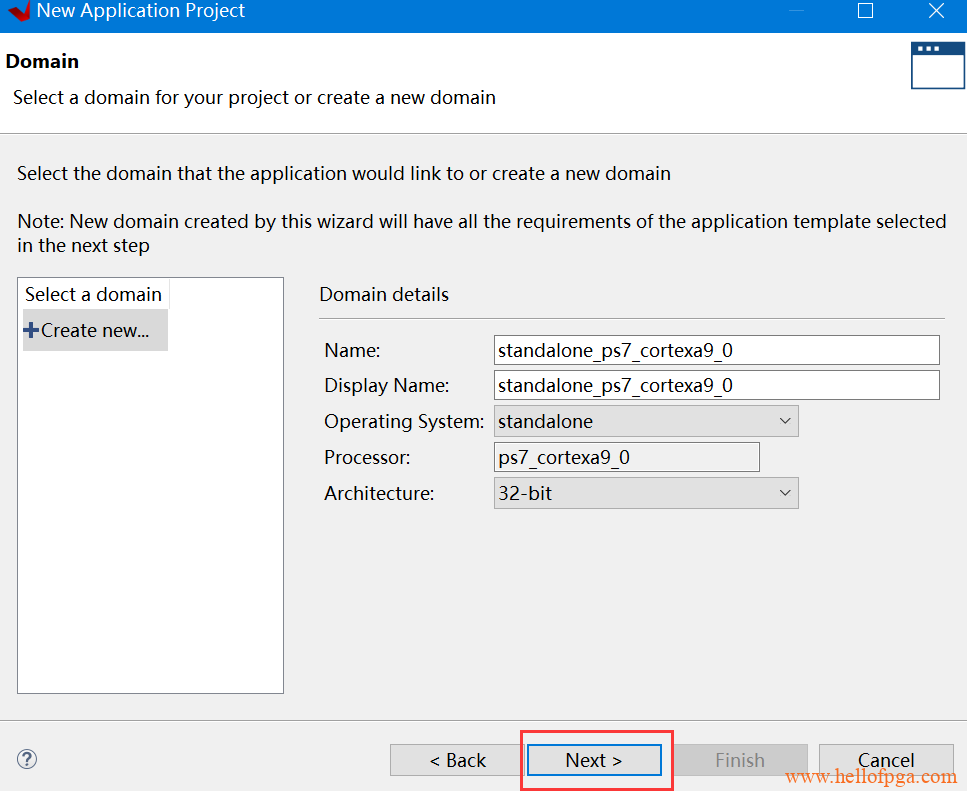

6) 选择next

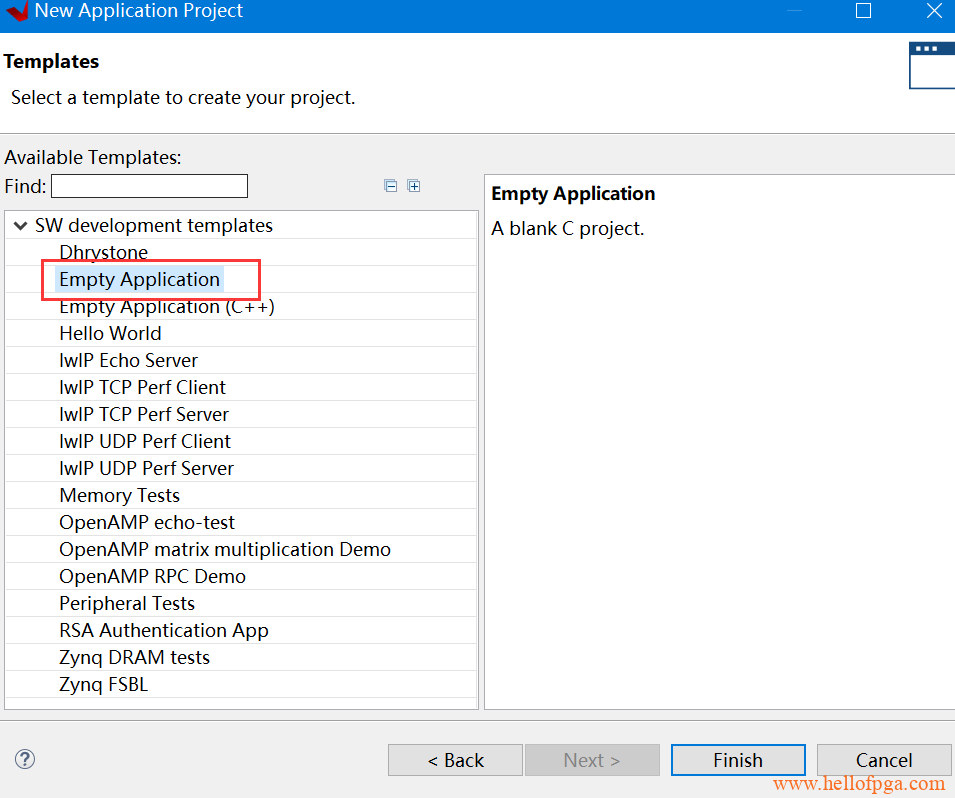

7) 选择创建一个空工程

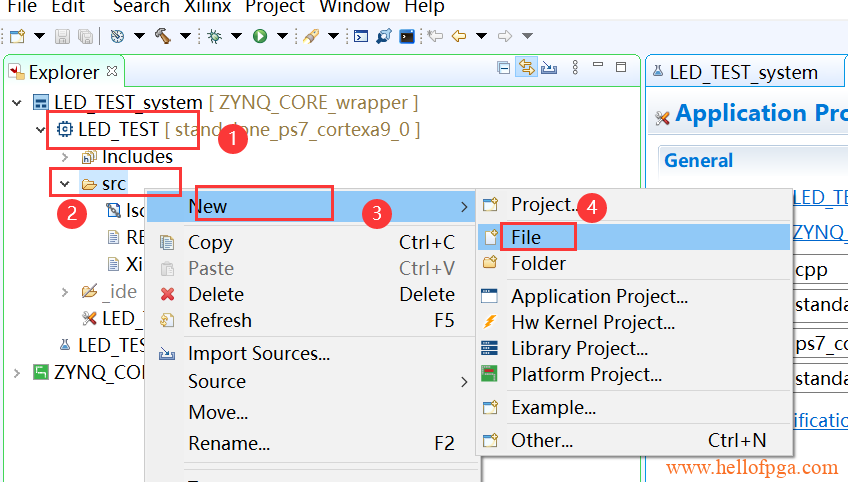

8)在工程中添加main.c文件 src—>New—>File 如下图所示

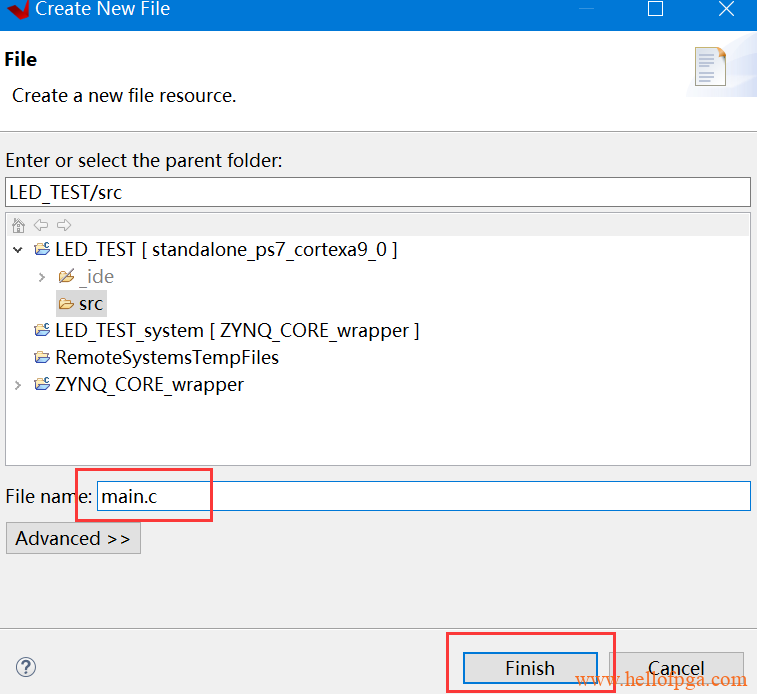

9)在弹出的窗口中填入main.c 并且保存

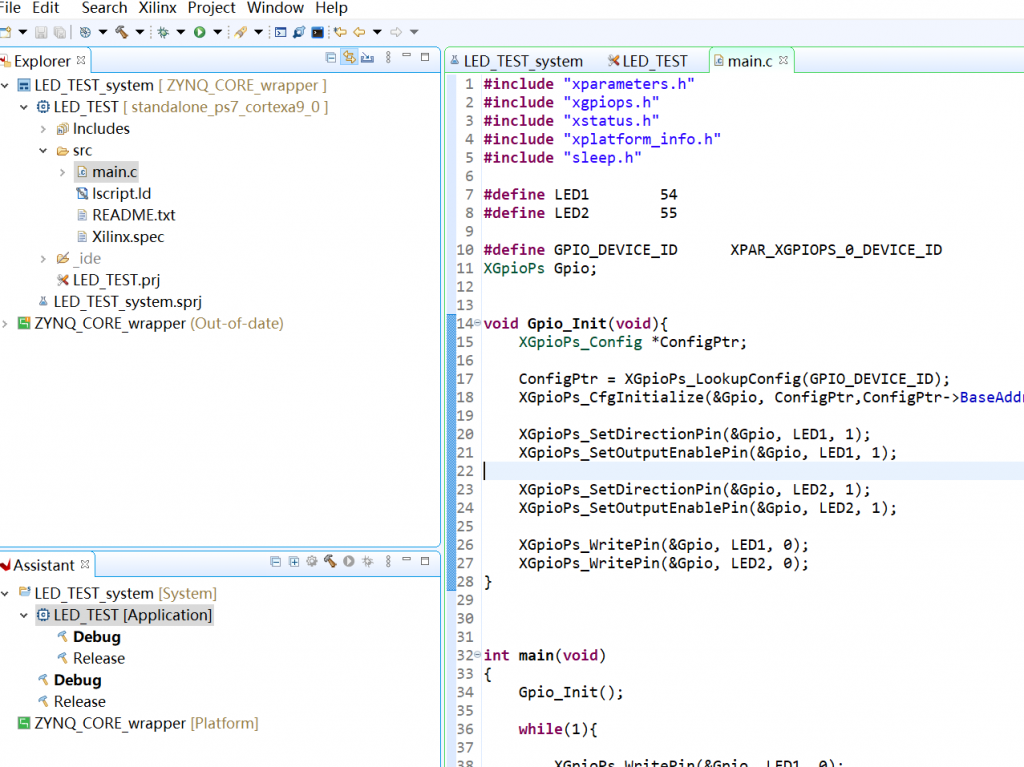

10).打开刚才创建的main.c 然后 写入以下代码

有一个地方值得注意 EMIO的 IO口编号 是从54开始的,也就是我VIVADO 下创建的 EMIO端口,在PS端都是从54-55-56 依次排序的(小贴士 小于54的是MIO 也就是芯片PS的硬件IO口)

#include "xparameters.h"

#include "xgpiops.h"

#include "xstatus.h"

#include "xplatform_info.h"

#include "sleep.h"

#define LED1 54

#define LED2 55

#define GPIO_DEVICE_ID XPAR_XGPIOPS_0_DEVICE_ID

XGpioPs Gpio;

void Gpio_Init(void){

XGpioPs_Config *ConfigPtr;

ConfigPtr = XGpioPs_LookupConfig(GPIO_DEVICE_ID);

XGpioPs_CfgInitialize(&Gpio, ConfigPtr,ConfigPtr->BaseAddr);

XGpioPs_SetDirectionPin(&Gpio, LED1, 1);

XGpioPs_SetOutputEnablePin(&Gpio, LED1, 1);

XGpioPs_SetDirectionPin(&Gpio, LED2, 1);

XGpioPs_SetOutputEnablePin(&Gpio, LED2, 1);

XGpioPs_WritePin(&Gpio, LED1, 0);

XGpioPs_WritePin(&Gpio, LED2, 0);

}

int main(void)

{

Gpio_Init();

while(1){

XGpioPs_WritePin(&Gpio, LED1, 0);

XGpioPs_WritePin(&Gpio, LED2, 0);

sleep(1);

XGpioPs_WritePin(&Gpio, LED1, 1);

XGpioPs_WritePin(&Gpio, LED2, 1);

sleep(1);

};

return 0;

}

下载到板子上进行验证

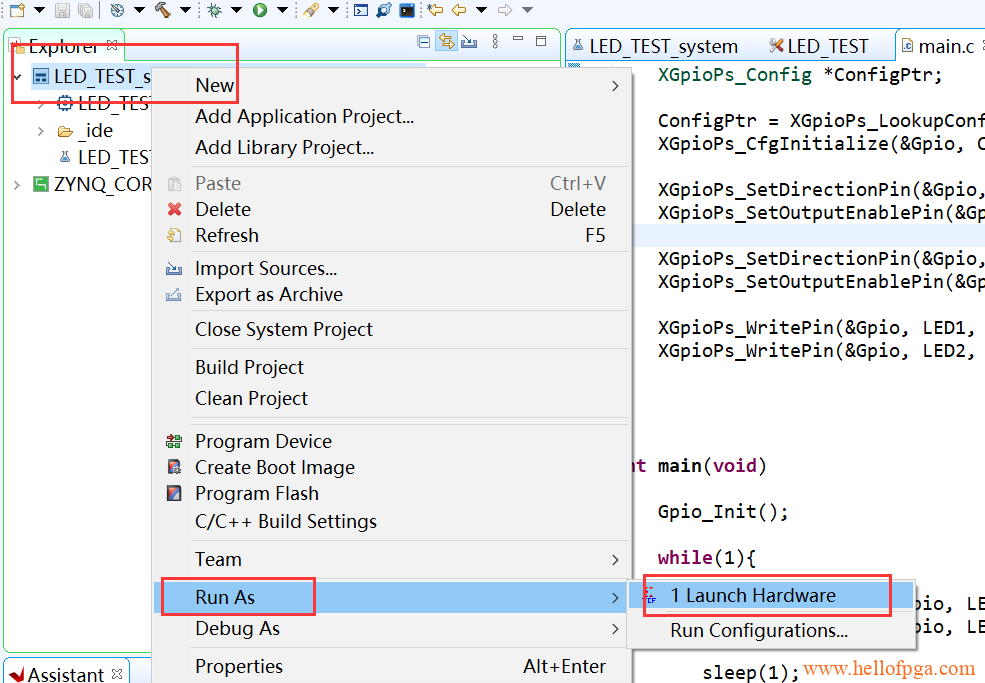

选中我们生成的LED_TEST工程 展开绿色箭头(RUN)右边的图标,选择Run As→1 Launch on Hardware

可以看到板子上的LED灯在闪烁

备注

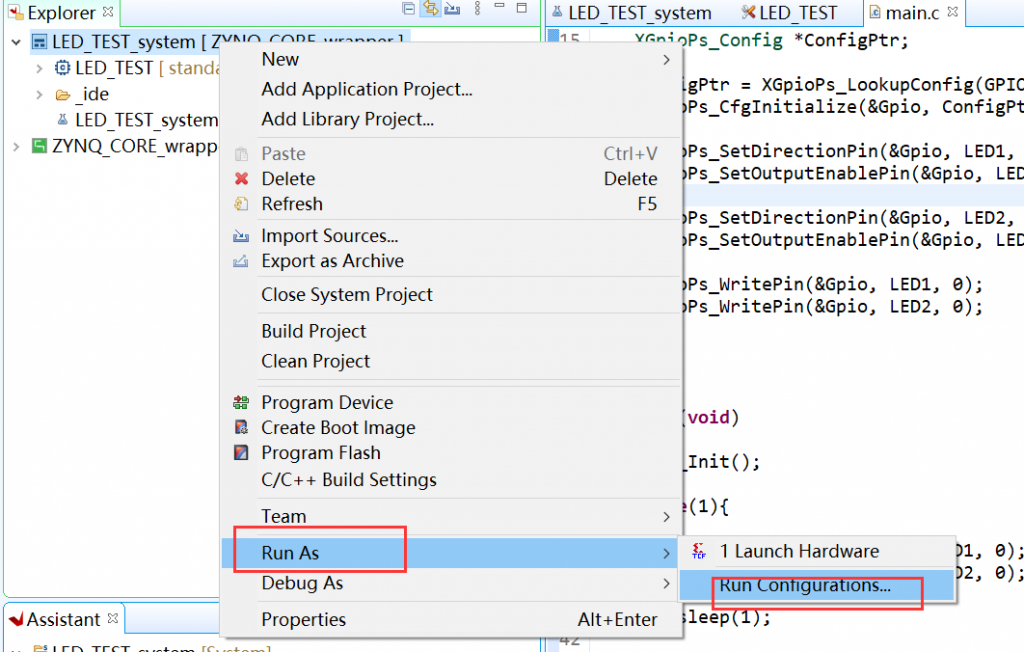

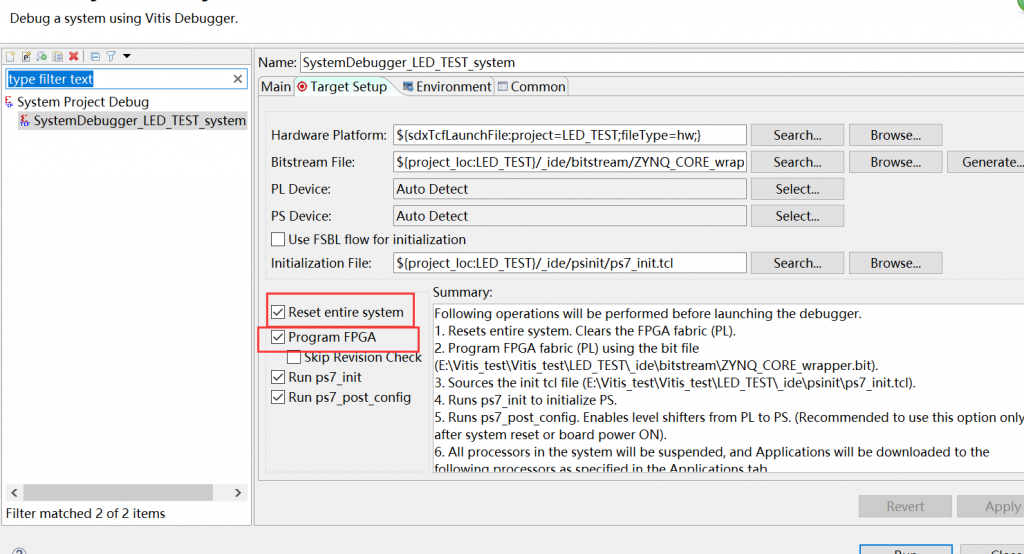

如果程序没有按预期运行,请检查FPGA程序有没有设置自动加载,右键我们的工程,然后Run As→Run Configurations 配置

并将Reset entire system 和 Program FPGA 的勾都勾上,再选run 尝试

以上是vivado 2020.2版本 的简单vitis 演示,如果是其他带vitis 版本的vivado ,操作上可能会有些许区别,请自行研究尝试。

你好,我用的vivado 2023.2,Smart ZYNQ SP版,在Vitis中Program Flash的时候初始化QSPI失败:Zynq> ERROR: [Xicom 50-186] Error while detecting SPI flash device – unrecognized JEDEC id bytes: 40, 66, fd

检查下 PROGRAM FLASH 中的FLASH TYPE 和我写的是否一致, 另外 VIVADO 里也检查一下 QSPI 相关的设置看看。 如果还有问题,就先用我工程中的 FSBL.ELF 和 BIN 测试看看